Johannes Gutenberg-Universität Mainz Institut für Physik, Experimentelle Teilchen- und Astroteilchen-Physik

# Diplomarbeit

# Entwicklung eines Datenerfassungssystems für die Auslese des TimePix-Chips

Michael Zamrowski

August 2009

Betreuer: Prof. Dr. Stefan Tapprogge

# Inhaltsverzeichnis

| Eir | nleitur | ng       |                                                             | ix |

|-----|---------|----------|-------------------------------------------------------------|----|

| 1   | Phys    | ikalisch | e Grundlagen                                                | 1  |

|     | 1.1     | Intern   | ationaler Linearbeschleuniger                               | 1  |

|     |         | 1.1.1    | Beschleuniger des International Linear Collider (ILC)       | 2  |

|     |         | 1.1.2    | Anforderung an die Detektoren für den ILC                   | 5  |

|     | 1.2     | Zeitpr   | ojektionskammern                                            | 6  |

|     |         | 1.2.1    | Wechselwirkung von Teilchen mit Materie                     | 7  |

|     |         | 1.2.2    | Spurrekonstruktion durch Zeitprojektion                     | 8  |

|     |         | 1.2.3    | Gasverstärkung mit GEM-Stapeln                              | 9  |

|     |         | 1.2.4    | Anforderungen an die Zeitprojektionskammern für den ILC     | 10 |

| 2   | Time    | Pix-Chip | <b>5</b>                                                    | 13 |

|     | 2.1     | Aufbai   | u des TimePix-Chips                                         | 13 |

|     | 2.2     | Analog   | ge Verarbeitung der Signale                                 | 15 |

|     |         | 2.2.1    | Vorverstärker                                               | 16 |

|     |         | 2.2.2    | Diskriminator                                               | 16 |

|     | 2.3     | Digita   | le Verarbeitung der Signale                                 | 18 |

|     |         | 2.3.1    | TimePix-Synchronisationslogikschaltung                      | 19 |

|     |         | 2.3.2    | Funktion des Schieberegisters einer Matrixzelle             | 21 |

|     | 2.4     | Steuer   | ung des TimePix-Chips über die Ein- und Ausgabeeinheit      | 21 |

|     |         | 2.4.1    | Steuerung der Strom- und Spannungsquellen des TimePix-Chips | 23 |

|     |         | 2.4.2    | Lese- und Schreiboperationen der Matrix                     | 23 |

|     |         | 2.4.3    | Einkopplung von Testpulsen in den TimePix-Chip              | 24 |

| 3   | Tech    | nische G | Grundlagen                                                  | 25 |

|     | 3.1     | Konfig   | gurierbare Logik                                            | 25 |

|     |         | 3.1.1    | Programmierbarer integrierter Schaltkreis (FPGA)            | 25 |

|     |         | 3.1.2    | Beschreibungssprachen der Schaltkreisstrukturen im FPGA     | 27 |

|     |         | 3.1.3    | Entwicklungswerkzeuge                                       | 27 |

|     | 3.2     | Dateni   | übertragung über Netzwerke                                  | 27 |

|     |         | 3.2.1    | Netzwerkschichtenmodell                                     | 28 |

|     |         | 3.2.2    | Gigabit-Ethernet                                            | 28 |

|     |         | 3.2.3    | Netzwerkprotokolle                                          | 29 |

| 4   | Entw   | ricklung eines verbesserten Datenerfassungssystems für den TimePix-Chip          | 33 |

|-----|--------|----------------------------------------------------------------------------------|----|

|     | 4.1    | Anforderungen an das Auslesesystem                                               | 33 |

|     |        | 4.1.1 Anforderungen aufgrund der TimePix-Chip-Spezifikationen                    | 33 |

|     |        | 4.1.2 Anforderungen an die Benutzerfreundlichkeit des endgültigen Systems        | 34 |

|     | 4.2    | Bestehendes Auslesesystem                                                        | 34 |

|     |        | 4.2.1 Überblick über das MUROS2 System                                           | 34 |

|     |        | 4.2.2 Beschränkungen des MUROS2                                                  | 35 |

|     | 4.3    | Aufbau des Auslesesystems                                                        | 36 |

|     |        | 4.3.1 Funktion des Steckadapters zwischen TimePix-Chip und FPGA                  | 37 |

|     |        | 4.3.2 Entwicklungsplatine                                                        | 39 |

|     |        | 4.3.3 VHDL-Programm zur Konfiguration des FPGAs                                  | 40 |

|     |        | 4.3.4 Steuerungs- und Ausleseprogramm                                            | 42 |

|     | 4.4    | Funktionsweise des VHDL-Programms bei der Datenerfassung                         | 43 |

|     | 4.5    | Gleichzeitige Auslese mehrerer TimePix-Chips                                     | 47 |

| 5   | Über   | prüfung der Systemfunktion                                                       | 49 |

|     | 5.1    | Simulation des VHDL-Programms                                                    | 49 |

|     | 5.2    | Messung einzelner Funktionskomponenten zur Überprüfung der Simulationsergebnisse | 52 |

|     |        | 5.2.1 Untersuchung der Kommunikation zwischen Entwicklungsplatine und Rechner    | 52 |

|     |        | 5.2.2 Messung der Steuersignale an den TimePix-Chip                              | 53 |

|     |        | 5.2.3 Messung der Datensignale vom und zum TimePix-Chip                          | 54 |

|     | 5.3    | Korrektur der Bitanordnung im FSR                                                | 56 |

|     | 5.4    | Messungen am Gesamtsystem                                                        | 57 |

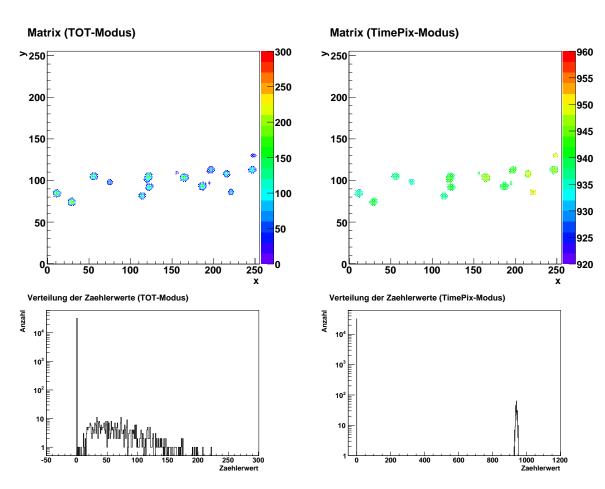

|     |        | 5.4.1 Überprüfung der Funktionen durch Messungen mit Rauschen                    | 58 |

|     |        | 5.4.2 Messungen mit dem Testpulsgenerator                                        | 64 |

|     |        | 5.4.3 Messungen mit niederfrequenter elektromagnetischer Strahlung               | 66 |

| 6   | Inbe   | triebnahme des Auslesesystems an der Zeitprojektionskammer                       | 69 |

|     | 6.1    | Aufbau des Experiments zur Erfassung der kosmischen Strahlung                    | 69 |

|     |        | 6.1.1 Aufbau des Zeitprojektionskammerprototypen                                 | 69 |

|     |        | 6.1.2 Erzeugung des Auslösersignals                                              | 70 |

|     | 6.2    | Durchführung der Experimente an der Zeitprojektionskammer                        | 71 |

|     |        | 6.2.1 Vorbereitende Versuche zur Systemüberprüfung                               | 72 |

|     |        | 6.2.2 Aufnahme von Spuren kosmischer Teilchen                                    | 72 |

|     |        | 6.2.3 Ermittlung der Ausleserate                                                 | 83 |

|     | 6.3    | Ergebnisse der Messungen                                                         | 84 |

| 7   | Zusa   | mmenfassung und Ausblick                                                         | 87 |

| An  | hang   |                                                                                  | 89 |

| Lit | eratur | verzeichnis                                                                      | 93 |

# Abbildungsverzeichnis

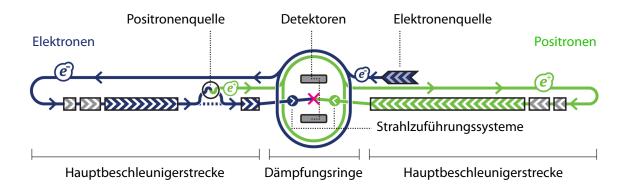

| 1.1  | Schematischer Aufbau des International Linear Colliders                            | 3  |

|------|------------------------------------------------------------------------------------|----|

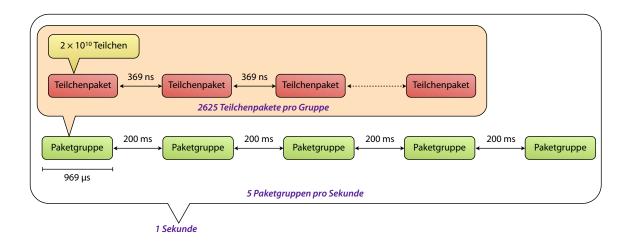

| 1.2  | Struktureller Aufbau der Teilchenpakete im ILC                                     | 5  |

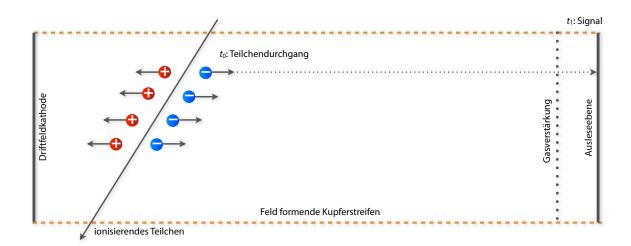

| 1.3  | Funktionsweise einer Zeitprojektionskammer                                         | 8  |

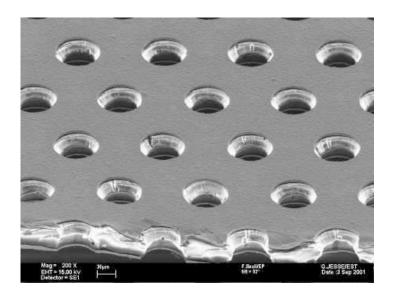

| 1.4  | Elektronenmikroskopaufnahme eines GEMs                                             | 9  |

| 2.1  | Foto des TimePix-ASIC mit der für die Auslese konzipierten Trägerplatine           | 14 |

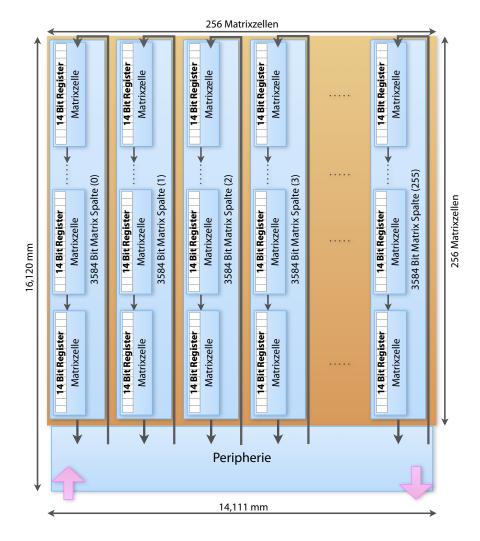

| 2.2  | Schematischer Aufbau des TimePix-Chips                                             | 14 |

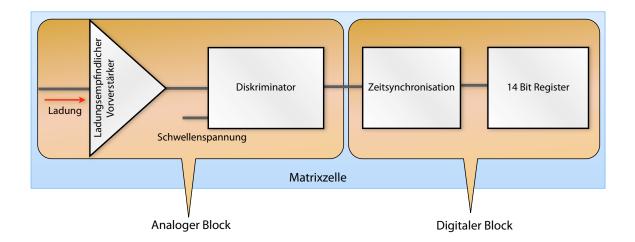

| 2.3  | Schematische Darstellung der Arbeitsweise der Matrixzellen                         | 15 |

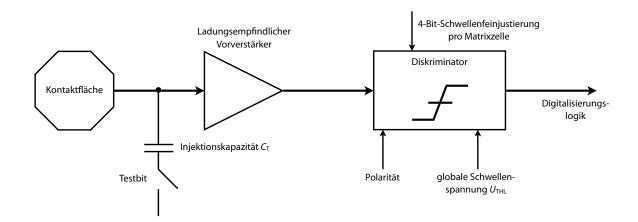

| 2.4  | Schema der analogen Sektion einer Matrixzelle                                      | 16 |

| 2.5  | Schematische Darstellung der Signalverarbeitung im Diskriminator                   | 17 |

| 2.6  | Blockschaltbild des Diskriminators                                                 | 18 |

| 2.7  | Schema der digitalen Sektion einer Matrixzelle                                     | 19 |

| 2.8  | Funktionsprinzip der Signalverarbeitung des Diskriminatorsignals                   | 20 |

| 2.9  | Schematische Darstellung der Peripherie des TimePix-Chips                          | 22 |

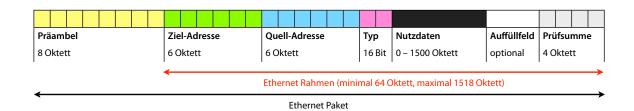

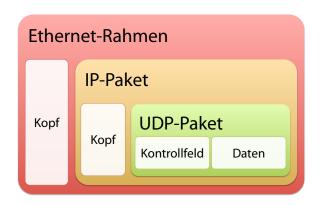

| 3.1  | Ethernet-Datenblockformat                                                          | 29 |

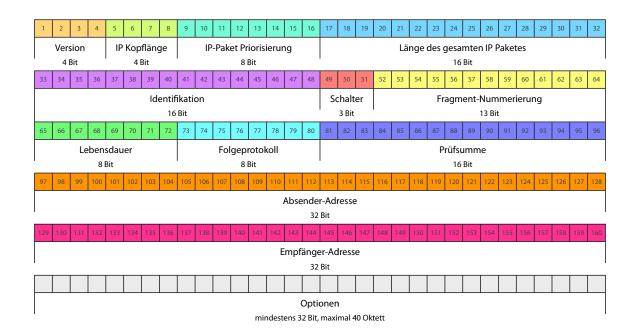

| 3.2  | Aufbau des Kopfdatenbereichs eines IP-Paketes                                      | 30 |

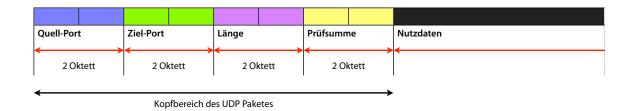

| 3.3  | Aufbau des Kopfdatenbereichs eines UDP-Paketes                                     | 31 |

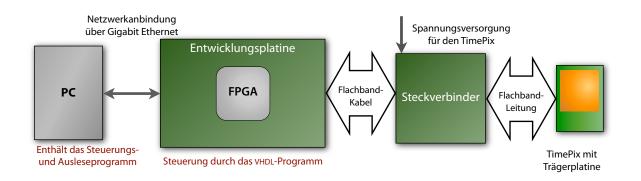

| 4.1  | Blockdiagramm des Auslesesystems                                                   | 36 |

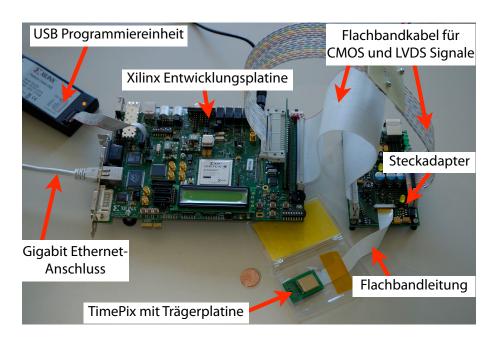

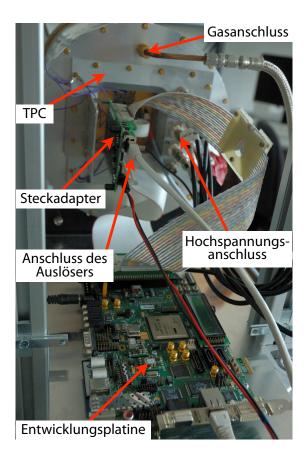

| 4.2  | Foto des Aufbaus des Auslesesystems                                                | 37 |

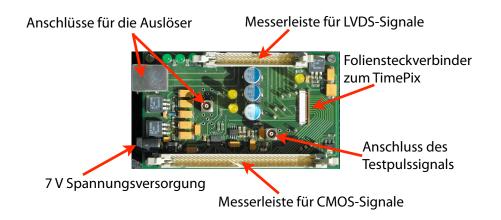

| 4.3  | Foto des Steckadapters                                                             | 38 |

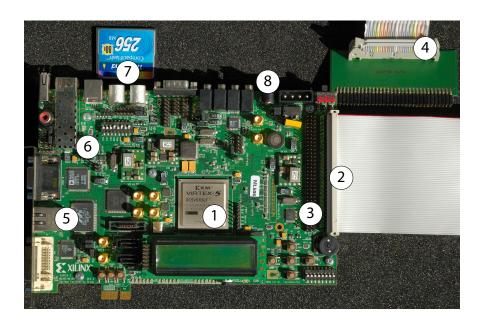

| 4.4  | Foto der Xilinx Entwicklungsplatine mit FPGA                                       | 39 |

| 4.5  | Schematischer Aufbau des Datenstroms bei der Ethernet-Kommunikation                | 40 |

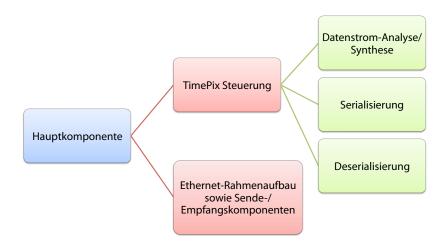

| 4.6  | Schematische Darstellung der einzelnen Komponenten des VHDL-Programms              | 41 |

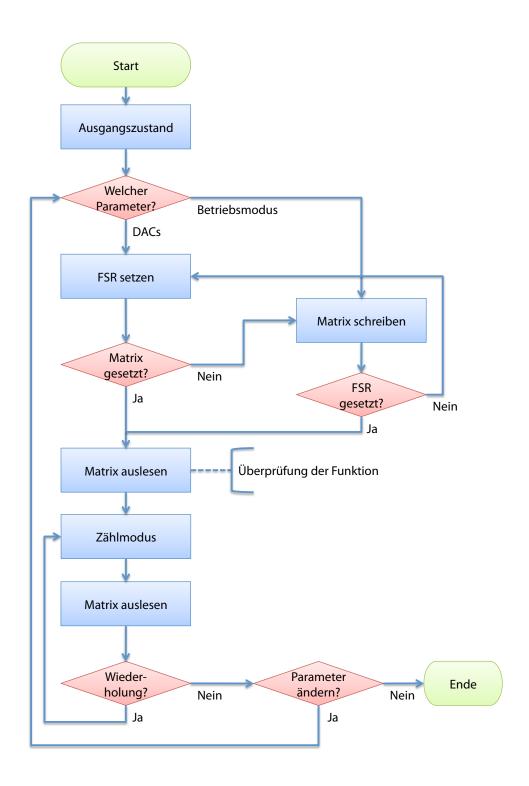

| 4.7  | Flussdiagramm zur Verdeutlichung der Abläufe bei einer Datenerfassung              | 44 |

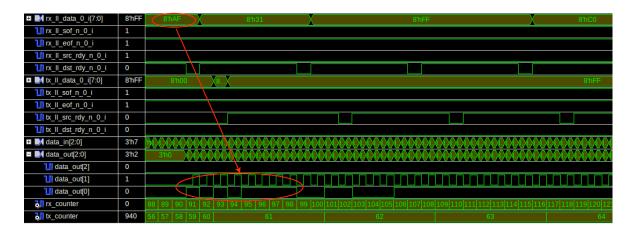

| 5.1  | Simulation der Enternet Kommunikation                                              | 50 |

| 5.2  | Simulation der Steuersignale an den TimePix                                        | 51 |

| 5.3  | Simulation der Serialisierung/Deserialisierung von Daten an/vom TimePix-Chip       | 52 |

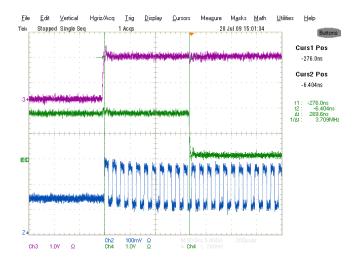

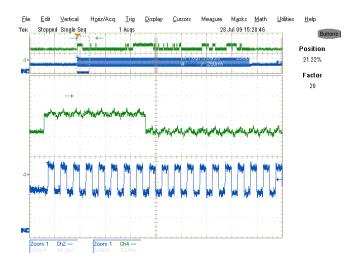

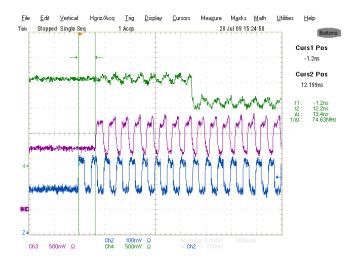

| 5.4  | Oszilloskopbild der Steuersignale beim Setzen des TimePix-Chips in den Zählmodus . | 53 |

| 5.5  | Oszilloskopbild der Datensignale zum TimePix-Chip                                  | 54 |

| 5.6  | Verzögerungsmessung der empfangenden TimePix-Daten mit Hilfe des Oszilloskops .    | 55 |

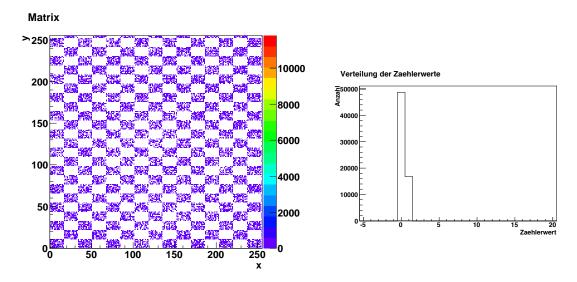

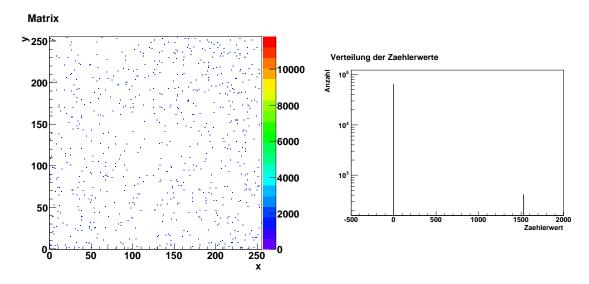

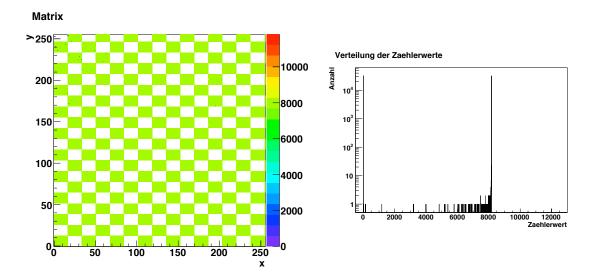

| 5.7  | Aufnahme des Rauschens im Eintreffer-Modus                                         | 59 |

| 5.8  | Aufnahme des Rauschens im Ankunftszeit-Modus bei einer Schwelle von THL = $350$ .  | 60 |

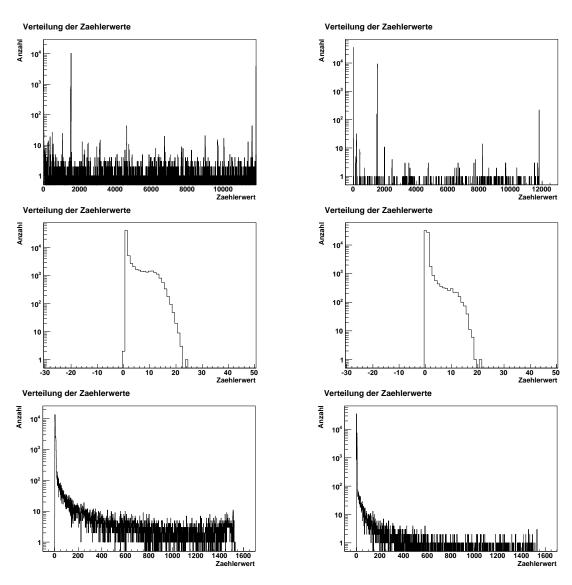

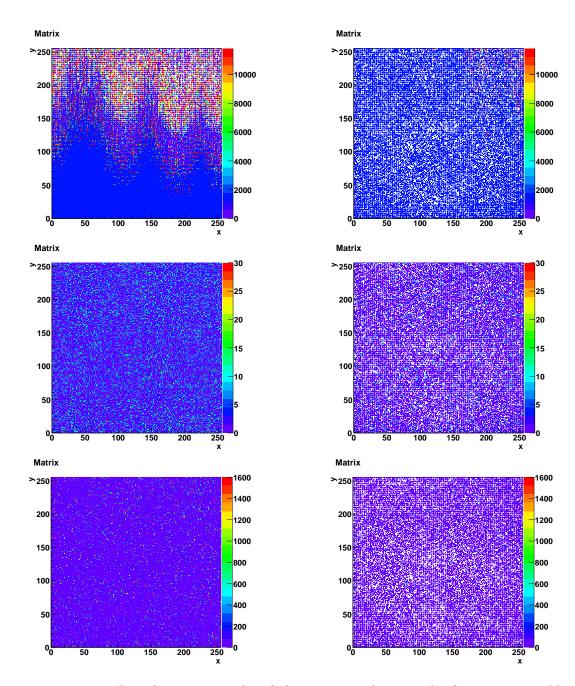

| 5.9  | Zählstände bei Rauschen im Ankunftszeit-, Ereigniszähl- und TOT-Modus              | 61 |

| 5.10 | Matrix bei Aufnahme des Rauschens im Ankunftszeit-, Ereigniszähl- und TOT-Modus    | 62 |

| 5.11 | Mehrfachbelichtete Aufnahmen des Rauschens im Ereigniszähl-Modus                                           | 63 |

|------|------------------------------------------------------------------------------------------------------------|----|

| 5.12 | Aufnahmen des Rauschens im Ankunftszeit-Modus für $t_2 = 3,75 \mu\text{s}$                                 | 64 |

| 5.13 | Bild der Matrix nach Einkoppeln von Testpulsen im Ereigniszähl-Modus                                       | 65 |

| 5.14 | Schreiben des japanischen Silbenzeichens な auf den TimePix-Chip                                            | 66 |

| 6.1  | Foto des an den Feldkäfig angeschlossenen Auslesesystems                                                   | 71 |

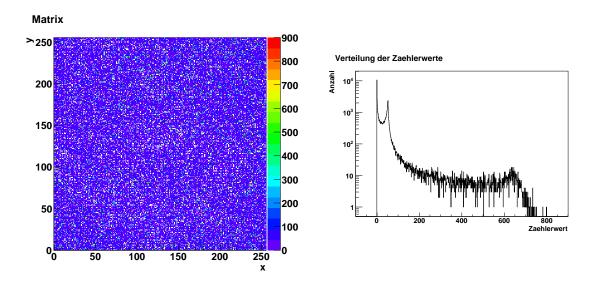

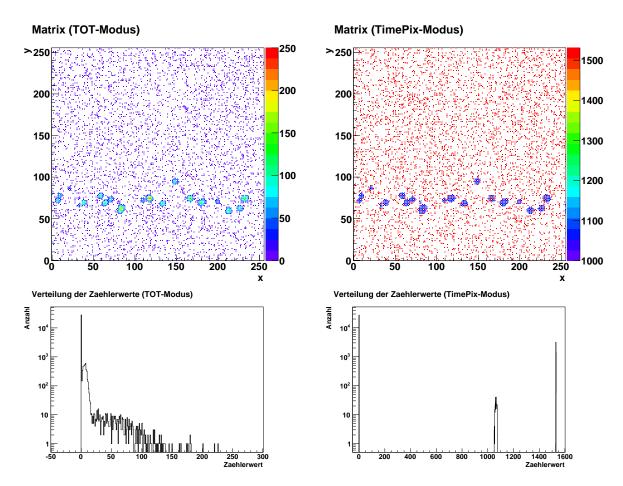

| 6.2  | Aufnahme des Rauschens in der TPC                                                                          | 73 |

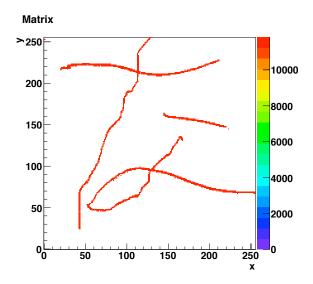

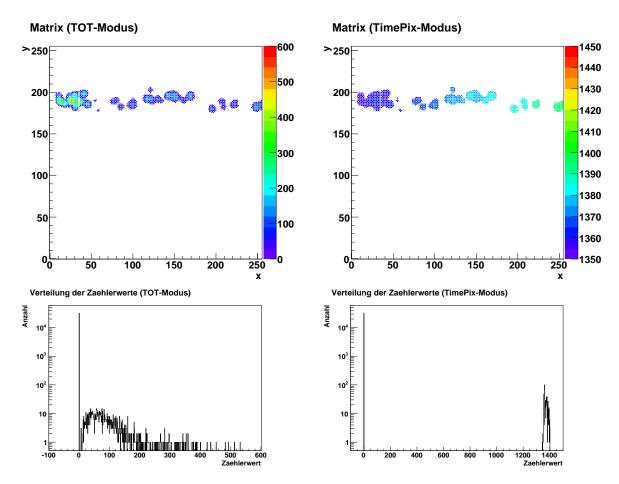

| 6.3  | Aufnahme einer Spur bei einer Schwelle von 348 und $s_{\text{Drift}} \approx 12,45 \text{ cm} \dots \dots$ | 74 |

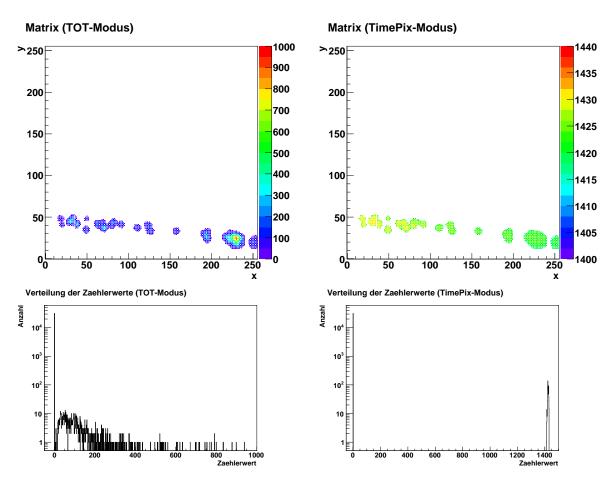

| 6.4  | Aufnahme einer Spur bei einer Schwelle von 348 und $s_{\text{Drift}} \approx 2,79 \text{ cm}$              | 75 |

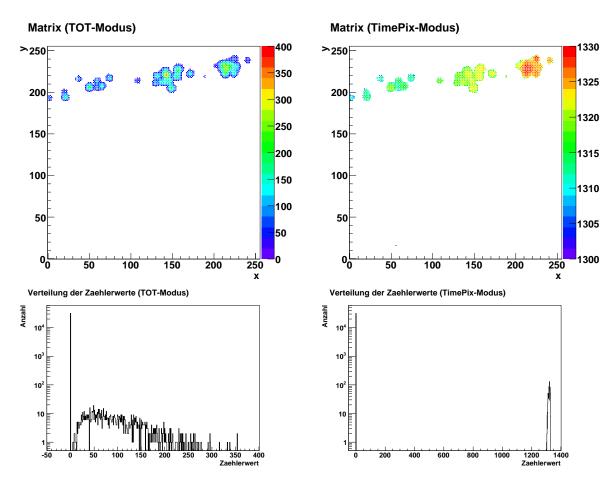

| 6.5  | Aufnahme einer Spur bei einer Schwelle von 348 und $s_{\text{Drift}} \approx 2,14 \text{ cm}$              | 76 |

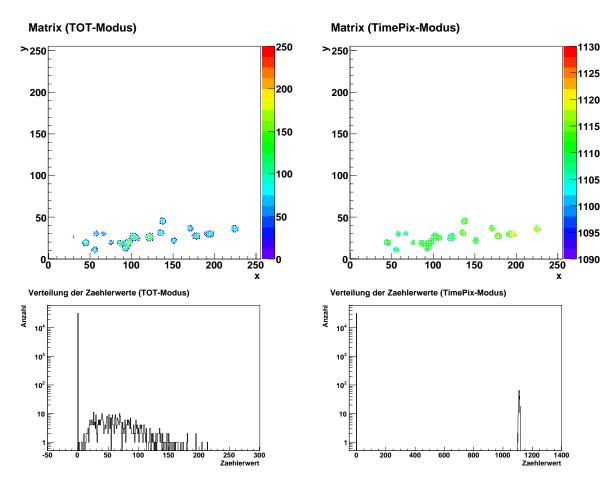

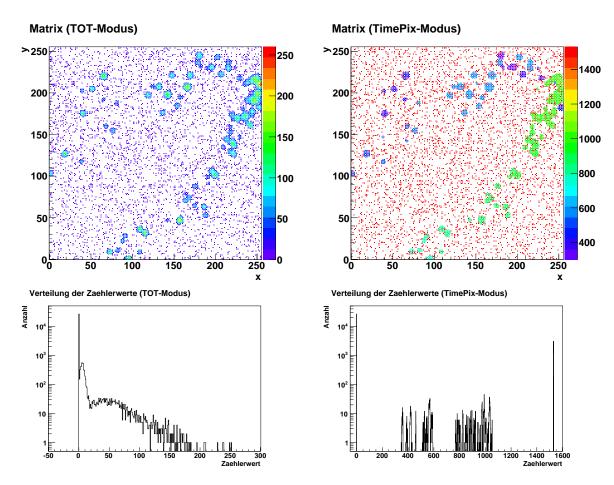

| 6.6  | Aufnahme einer Spur bei einer Schwelle von 348 und $s_{\text{Drift}} \approx 4,40 \text{ cm}$              | 77 |

| 6.7  | Aufnahme einer Spur bei einer Schwelle von 348 und $s_{\text{Drift}} \approx 8,91 \text{ cm}$              | 78 |

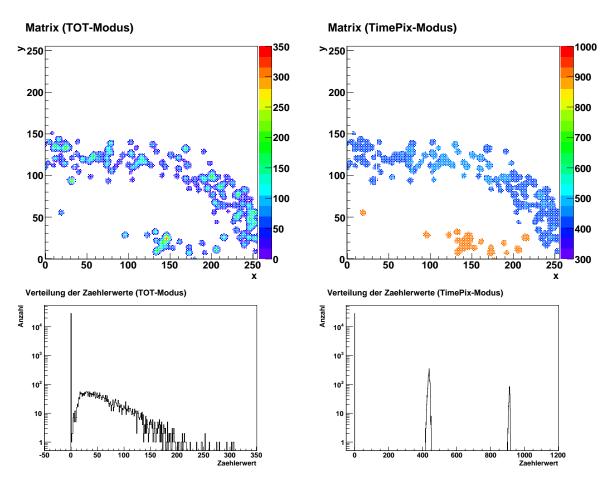

| 6.8  | Aufnahme einer Spur bei einer Schwelle von 330 und $s_{\text{Drift}} \approx 9,23 \text{ cm}$              | 79 |

| 6.9  | Aufnahme einer Spur bei einer Schwelle von 330 und $s_{\text{Drift}} \approx 11,38 \text{ cm} \dots \dots$ | 80 |

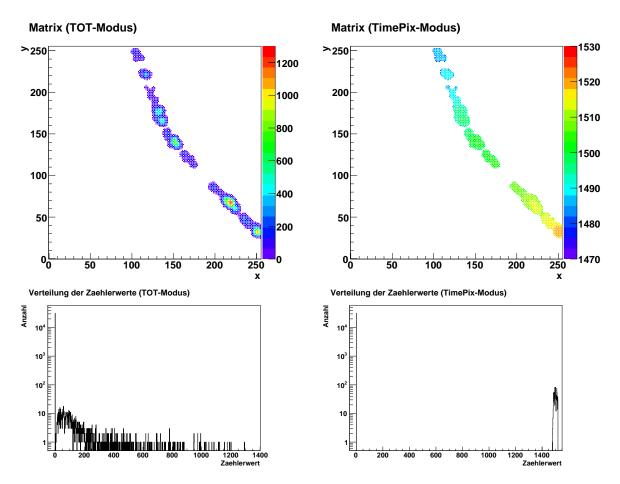

| 6.10 | Aufnahme einer Spur bei einer Schwelle von 348 und $s_{\text{Drift}} \approx 0.21 \text{ cm}$              | 81 |

| 6.11 | Aufnahme einer Spur bei einer Schwelle von 348 und $s_{\text{Drift}} \approx 13,52 \text{ cm} \dots \dots$ | 82 |

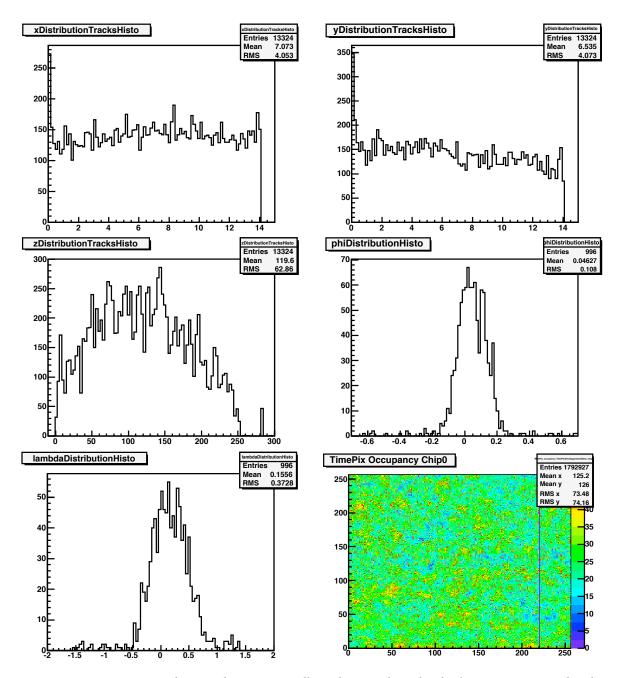

| 6.12 | Auswertung des Messdaten                                                                                   | 85 |

# **Tabellenverzeichnis**

| 1.1 | Die nominalen Parameter des Beschleunigers für den International Linear Collider | 4  |

|-----|----------------------------------------------------------------------------------|----|

| 1.2 | Anforderungen an eine Zeitprojektionskammer für den ILC                          | 10 |

| 2.1 | Die vier Betriebsmodi einer Matrixzelle                                          | 21 |

| 2.2 | Die Betriebszustände des TimePix-Chips                                           | 22 |

| 5.1 | Inhalt des FSR nach der Auswertung der Messung                                   | 57 |

| 5.2 | Konfiguration der Strom- und Spannungswerte des TimePix-Chips                    | 58 |

| 6.1 | Vergleich der gemessenen maximalen Ausleseraten                                  | 82 |

## **Einleitung**

Das Ziel der Teilchenphysik ist die Erforschung der kleinsten Teilchen des Universums. Nach der Entdeckung des Atoms und des Atomkern und der Entwicklung von Theorien, welche die Teilchen gut erklären können, liegt der Schwerpunkt der wissenschaftlichen Arbeiten auf den Elementarteilchen.

Gegenwärtig liefert das Standardmodell der Teilchenphysik das Verständnis für die Elementarteilchen und ihrer Wechselwirkungen und ermöglicht eine Beschreibung und richtige Vorhersage vieler physikalischer Prozesse in der Hochenergiephysik. Trotz der Erfolge des Standardmodells bleiben einige Fragen offen und können von der Theorie nicht vollständig erklärt werden. So ist die vierte bekannte fundamentale Kraft, die Gravitation, nicht im Standardmodell beschrieben. Ebenso ist der Mechanismus, der zur spontanen Symmetriebrechung in der elektroschwachen Wechselwirkung führt und den W<sup>±</sup>- und Z<sup>0</sup>-Bosonen ihre Masse verleiht, nicht ausreichend verstanden. Der Higgs-Mechanismus aus der theoretischen Physik führt daher ein skalares Feld und ein mit dem Feld assoziiertes Teilchen ein, das Higgs-Teilchen, um damit die Symmetriebrechung und den Massenmechanismus zu verstehen. Allerdings konnte bisher in keinem Experiment dieses Teilchen nachgewiesen werden. Aber auch ein um das Higgs-Boson erweitertes Standardmodell lässt viele Probleme unbeantwortet. Dazu gehören die Fragen wieso das Universum zum Großteil aus dunkler Materie besteht und die Materie-Antimaterie-Asymmetrie. Der Nachweis der Existenz der Neutrino-Oszillation führt zu der Tatsache, dass Neutrinos eine von Null verschiedene Ruhemasse besitzen müssten, was allerdings weitreichende Konsequenzen für das Standardmodell hätte. Eine weitere Möglichkeit zum Verständnis der Teilchenphysik in der theoretischen Physik liefern supersymmetrische Modelle. Diese Supersymmetrische Theorie beantwortet einige Probleme des Standardmodells. Allerdings gibt es keinen Beweis für diese Modelle, insbesondere wurde kein von diesen Theorien vorhergesagtes Teilchen beobachtet.

In den Bemühungen ein umfassendes Verständnis der Elementarteilchen zu entwickeln, werden in der Experimentalphysik Teilchenbeschleuniger entwickelt, welche Energien in einem bisher ungekanntem Ausmaß erreichen. Mit dem *Large Hadron Collider* wird ein Teilchenbeschleuniger in Betrieb genommen, an dem Teilchenkollisionen mit einer Schwerpunktsenergie von bis zu 14 TeV stattfinden sollen. Der nächste große zukünftige Teilchenbeschleuniger soll ein Elektronen-Positronen-Linearbeschleuniger, der *International Linear Collider*, werden. Aufgrund der in ihm stattfindenden Reaktionen von Leptonen stellt der *International Linear Collider* eine Präzisionsmaschine dar, mit der Entdeckungen des *Large Hadron Colliders* sehr genau vermessen werden können.

Verbunden mit der Entwicklung solcher Teilchenbeschleuniger ist die Entwicklung von Detektoren, welche die Zerfallsprodukte bei der Kollision zweier Teilchen erfassen und vermessen sollen. An solche Detektoren werden hohe Anforderungen gestellt, damit diese das Potenzial des *International Linear Colliders* voll ausschöpfen können. Es wird daher im Bereich der Detektorentwicklung an mehreren Alternativen geforscht, um dem hohen Anspruch, welcher an den *International Linear Collider* und seine Detektoren gestellt wird, gerecht zu werden.

Eine Möglichkeit der Spurmessung in einem Detektor für den International Linear Collider bieten Zeitprojektionskammern. Außerdem stellen die Zeitprojektionskammern einen vielversprechen-

den Ansatz zur Realisierung der Impulsmessung mit der angestrebten Auflösung. In dem Gas einer Zeitprojektionskammer hinterlassen geladene Teilchen eine Spur von Elektronen-Ionen-Paaren. Mit Hilfe von Gasverstärkungsstrukturen werden die Elektronen in der Kammer verstärkt und an eine ladungsempfindliche Ausleseelektronik weitergeleitet. Eine Möglichkeit der Auslese besteht mit dem hochauflösenden TimePix-Chip.

Nachdem im ersten Kapitel dieser Arbeit mit der Beschreibung des *International Linear Colliders* und der Zeitprojektionskammer einige physikalische Grundlagen dargestellt werden, wird im zweiten Kapitel der Aufbau und die Funktionsweise des TimePix-Chips erklärt. Der Betrieb des TimePix-Chips und die Auslese seiner Daten ist der Gegenstand der weiteren Kapitel. Dafür werden im dritten Kapitel die technischen Grundlagen geschaffen.

Das vierte Kapitel dieser Arbeit beschreibt die Entstehung und den Aufbau des Datenerfassungssystems. Es beschreibt die einzelnen Komponenten des Auslesesystems und erläutert deren Funktion. Im fünften Kapitel wird das System auf seine Funktionsfähigkeit überprüft, bevor der Einsatz an der Zeitprojektionskammer erfolgt, welcher im sechsten Kapitel beschrieben wird. Dieses sechste Kapitel zeigt auch die ersten Ergebnisse der Spurmessungen, welche erstmals mit einem solchen Datenerfassungssystem durchgeführt wurden.

Der Schwerpunkt dieser Diplomarbeit lag in der Entwicklung und Untersuchung eines neuartigen Datenerfassungssystems für den TimePix-Chip. Es werden die ersten Schritte bei der Realisierung eines solchen Projektes vorgestellt und der erfolgreiche Einsatz des Datenerfassungssystems zur Auslese und Steuerung des TimePix-Chips demonstriert.

## 1 Physikalische Grundlagen

Für die Forschung in der experimentellen Teilchenphysik sind Teilchenbeschleuniger unerlässliche Instrumente. Aus der De-Broglie-Gleichung  $\lambda=\frac{h}{p}$  lässt sich erkennen, dass zur Auflösung immer kleinerer Strukturen höhere Impulse notwendig sind. Ebenso zeigt die Energie-Masse-Beziehung  $E=m\cdot c^2$ , dass zur Erzeugung immer schwererer Teilchen immer größere Energien benötigt werden. Erst die Entwicklung immer leistungsfähigerer Teilchenbeschleuniger erlaubt die Untersuchung der elementaren Bestandteile der Materie und der Wechselwirkungskräfte zwischen den Teilchen. Somit konnte in der Teilchenphysik das Standardmodell entwickelt werden, um die Materiebausteine und ihre Wechselwirkungen zu beschreiben. Das Standardmodell hat viele präzise Vorhersagen gemacht, wie zum Beispiel die des Top-Quarks, dessen Entdeckung im Jahre 1995 (Abe u. a., 1995) als Bestätigung diente. Obwohl das Standardmodell der Teilchenphysik das derzeitige Verständnis aller elementaren Teilchen und ihrer fundamentalen Wechselwirkungen beschreibt, lässt es einige Frage offen, welche schon in der Einleitung aufgelistet wurden. Durch den Bau von Teilchenbeschleunigern, welche höhere Energien liefern können, verspricht man sich Antworten auf diese Fragen.

Dieses Kapitel soll einen Überblick über die Hochenergiephysik mit dem geplanten internationalen Elektron-Positron-Linearbeschleuniger (ILC)<sup>1</sup> geben. Neben einer Beschreibung des ILC werden die Detektorkonzepte für den ILC kurz vorgestellt. Als Teil der Spurdetektion wird in diesem Kapitel auch die Physik mit Zeitprojektionskammern vorgestellt.

#### 1.1 Internationaler Linearbeschleuniger

Teilchenbeschleuniger bilden die Hauptwerkzeuge zur Untersuchung der Teilchenphysik. Dieser Abschnitt fasst daher kurz die Physik mit Ringbeschleunigern und Linearbeschleunigern zusammen und versucht die Motive für den Bau eines internationalen Elektronen-Positronen-Linear-Beschleunigers zu benennen.

Bisherige Experimente wurden überwiegend an Ringbeschleunigern durchgeführt. In Speicherringen werden Teilchenpakete in mehreren Umläufen beschleunigt und dann mehrfach an den Wechselwirkungspunkten zur Kollision gebracht. Sie haben somit den Vorteil zum Erreichen der endgültigen Energie die Beschleunigerstrecke mehrfach zu durch laufen und verschiedene Experimente an den diversen Wechselwirkungspunkten im Ring durchzuführen. Nachteilig ist jedoch, dass jedes Teilchen mit der Masse m während eines Umlaufs Energie in Form von Synchrotronstrahlung verliert. Für den Energieverlust  $\Delta E$  pro Umlauf gilt:

$$\Delta E \sim \left(\frac{E}{m}\right)^4 \cdot \frac{1}{R} \quad . \tag{1.1}$$

Die maximale Schwerpunktsenergie bei Ringbeschleunigern wird somit durch das Beschleunigungsvermögen pro Umlauf und den Radius *R* des Ringes begrenzt. Der größte Elektronen-Positronen-Be-

<sup>&</sup>lt;sup>1</sup>International Linear Collider.

schleuniger LEP<sup>2</sup> am *Conseil Européen pour la Recherche Nucléaire* (CERN) erreichte eine maximale Schwerpunktsenergie von 209 GeV. Die Hadron-Elektron-Ring-Anlage (HERA) am Deutschen Elektronen-Synchrotron (DESY) in Hamburg beschleunigte Elektronen auf eine Energie von 27,5 GeV und erreichte eine Schwerpunktsenergie von 318 GeV bei dem Zusammenstoß von Elektronen mit Protonen.

Die Vorgehensweise, die Schwerpunktsenergien zu erhöhen, besteht in der Verwendung von Teilchen mit einer großen Masse, da der Energieverlust durch Synchrotronstrahlung mit der vierfachen Potenz der Masse abnimmt. Im großem Hadronen-Speicherring LHC³ am CERN werden Protonen mit einer Schwerpunktsenergie von bis zu  $\sqrt{s} = 14$  TeV miteinander kollidieren (LHC The guide, 2008). Durch die massereichen Teilchen sind hier die Synchrotonstrahlungsverluste verglichen mit denen bei Speicherringen mit Elektronen wegen  $(m_e/m_p)^4 \approx 10^{-13}$  unbedeutend. Protonen besitzen jedoch eine Substruktur aus Quarks und Gluonen, von denen jedes einen gewissen Teil des Gesamtimpulses trägt. Daher treten nicht die Protonen als Ganzes in Wechselwirkung, sondern die Teile ihrer Substruktur. Dies erschwert die Bestimmung der Schwerpunktsenergie und der Impulse der beteiligten Teilchen. Die für die physikalisch interessanten Prozesse zugrunde liegende Schwerpunktsenergie ist damit viel kleiner als 14 TeV. Zudem ergibt sich aus der Vielzahl der bei jeder Kollision beteiligten Teilchen ein großer Untergrund, aus dem die zu untersuchenden physikalisch interessanten Ereignisse separiert werden müssen.

Leptonische Beschleuniger haben diese Probleme nicht. Die Anfangszustände der Reaktionen sind bekannt und der Untergrund ist im Vergleich zu dem hadronischer Beschleuniger vernachlässigbar. Beim Einsatz von Speicherringen mit elementaren Myonen ließen sich somit höhere Schwerpunktsenergien ohne die bekannten Probleme von Hadronenbeschleunigern erreichen. Nachteilig erweist sich hier allerdings die endliche Lebensdauer der Myonen.

Eine weitere Alternative, um die Verluste durch Synchrotronstrahlung zu verringern, ist die Vergrößerung des Radius R. Linearbeschleuniger besitzen einen unendlich großen Radius, wodurch die Energieverluste durch Synchrotronstrahlung kaum vorhanden sind. Beim Einsatz von Elektron-Positron-Linearbeschleunigern hat man zudem elementare stabile Teilchen mit genau bekannter Schwerpunktsenergie. Auch die Möglichkeit der Polarisation der Teilchen im Anfangszustand besteht (Janssen, 2004; Linzmaier, 2008; Krautscheid, 2008).

#### 1.1.1 Beschleuniger des International Linear Collider (ILC)

Der *International Linear Collider* (ILC) ist ein geplanter Elektron-Positron-Linearbeschleuniger, der sich in der Forschungs- und Entwicklungsphase befindet. Daher existiert noch kein endgültiger Aufbau und auch kein fester Standort.

Die Elektronen und Positronen sollen am ILC auf einer langen, geraden Bahn mit einer Gesamtlänge von rund 31 km beschleunigt und unter einem minimalen Kreuzungswinkel von 14 mrad in einem Wechselwirkungspunkt aufeinandertreffen. Es ist nur ein Wechselwirkungspunkt vorgesehen, der mit zwei Detektoren ausgestattet ist, die abwechselnd in den Strahl gerückt werden können. Durch diese zwei Experimente wird, verglichen mit Ringbeschleunigern, die integrierte Luminosität nicht verdoppelt.

<sup>&</sup>lt;sup>2</sup>engl. Large Electron-Positron Collider.

<sup>&</sup>lt;sup>3</sup>engl. Large Hadron Collider.

**Abbildung 1.1:** Schematischer Aufbau des International Linear Colliders. Dargestellt sind die Standorte für die Elektronenquelle und des Undulators zur Erzeugung der Positronen. Zusammen mit den Dämpfungsringen, welche einen Umfang von 6,7 km besitzen sollen, und den beiden Hauptbeschleunigungsstrecken für die Elektronen bzw. Positronen erreicht der ILC eine Gesamtlänge von rund 31 km (Linearcollider, 2009).

Die Schwerpunktsenergie ist durch die Länge der beiden Beschleunigungsstrecken begrenzt und soll vorerst 90 GeV bis 500 GeV betragen. In einer zweiten Ausbauphase des Beschleunigers soll die Schwerpunktsenergie auf 1 TeV erhöht werden. Bei diesem Ausbau müssten die beiden Hauptbeschleunigungsstrecken von rund 11 km auf rund 20 km verlängert werden. Im Vergleich zu einem Speicherring müssen die Teilchen in einem Linearbeschleuniger bei einem Durchlauf der Beschleunigungsstrecke auf die volle Energie gebracht werden.

Der ILC bildet aufgrund seiner Ausrichtung eine ideale Ergänzung zum LHC. Die entgegengesetzte Ausrichtung von LHC und ILC ermöglicht die gegenseitige Ergänzung der beiden Projekte. Werden am LHC neue Teilchen entdeckt, können diese am ILC genauer untersucht werden. Wenn zum Bespiel ein leichtes Higgs-Boson existiert, wird es höchstwahrscheinlich am LHC entdeckt. Allerdings ist am LHC eine genaue Bestimmung der unterschiedlichen Kopplungen des Higgs Teilchens aufgrund der unbestimmten Anfangszustände kaum möglich. Dies würde dann zur wichtigen Aufgabe des ILC werden. Auch der bisher zugängliche Energiebereich kann genauer als bisher auf Abweichungen vom Standardmodell geprüft werden. Der ILC ist der erste leptonische Beschleuniger, der die Schwelle für Top-Antitop-Quark-Produktion bei etwa 350 GeV überschreitet und damit eine genaue Bestimmung der Masse und der elektroschwachen Eigenschaft des Top-Quarks ermöglicht. Dadurch könnten sich Hinweise auf neuartige Physik jenseits des Standardmodells ergeben (Krautscheid, 2008).

Abbildung 1.1 zeigt den schematischen Aufbau des internationalen Linearbeschleunigers. Der ILC wird eine Elektronenquellen enthalten, die einen bis zu 80 % polarisierten Elektronenstrahl erzeugt. Die polarisierten Positronen werden durch Paarbildung über den in den Elektronen-Hauptbeschleuniger integrierten Undulator erzeugt. Die so erzeugten Positronen verfügen über eine Polarisation von etwa 30 %, welche in einem späteren Ausbau auf etwa 60 % erhöht werden kann. Zur Reduktion der Emittanz werden die Strahlen in Elektronen- und Positronen-Dämpfungsringe mit einem Umfang von 6,7 km eingespeist. Die Extraktion der Strahlen aus den Speicherringen erfolgt bei einer Energie von 5 GeV in Form von gepulsten Ladungspaketen. Diese werden zu den zwei 11 km langen Hauptbeschleunigern, die mit einer Pulslänge von 1,6 ms arbeiten, transportiert. Hier erfolgt die eigentliche Beschleunigung mittels supraleitender Niob-Hohlraumresonatoren. Über das 4,5 km lange Strahlzuführungssystem erfolgt der Transport der Teilchenstrahlen von den Hauptbeschleunigern in den Detektor zu dem Wech-

selwirkungspunkt.

Die Qualität des Strahls wird durch seine Luminosität L beschrieben. Die Ereignisrate dN/dt ergibt sich dann zusammen mit dem Wirkungsquerschnitt  $\sigma_P$ , welcher von der Physik bei dem jeweiligen Prozess bestimmt ist:

$$\frac{\mathrm{d}N}{\mathrm{d}t} = \sigma_P(E) \cdot L \quad . \tag{1.2}$$

Zur präzisen Untersuchung von Prozessen mit hoher statistischer Signifikanz ist eine hohe Luminosität L notwendig:

$$L = \frac{N \, n_z f_{\text{Puls}}}{\sigma_x \, \sigma_y} \cdot H_D \quad . \tag{1.3}$$

Dabei sind  $\sigma_x$  und  $\sigma_y$  die mittlere transversale Breite der gaußförmigen Teilchenpakete, N ist die Anzahl der Teilchen pro Paket,  $n_z$  ist die Anzahl der Pakete in einer Gruppe,  $f_{\text{Puls}}$  ist die Pulsrate und  $H_D$  ist der Strahl-Strahl-Interaktionsfaktor (Janssen, 2004; Stöver, 2007).

Die angestrebte Luminosität bei 500 GeV soll  $2 \cdot 10^{34}$  cm<sup>-2</sup> s<sup>-1</sup> betragen. Der Strahl besteht aus einer Folge von Paketgruppen<sup>4</sup> mit einer Pulsrate von 5 Hz. Jede Paketgruppe mit der Pulslänge von 1 ms besteht aus rund 3000 Teilchenpaketen<sup>5</sup>. Jedes Teilchenpaket enthält bis zu  $2 \cdot 10^{10}$  Elektronen oder Positronen, die paketweise zur Kollision gebracht werden (Brau u. a., 2007). In Tabelle 1.1 sind einige Strahleigenschaften des ILC aufgeführt. In Abbildung 1.2 ist die Struktur der Teilchenpakete verdeutlicht.

**Tabelle 1.1:** Die nominalen Parameter des Beschleunigers für den International Linear Collider. Die nominalen Werte ergeben sich bei einer Schwerpunktsenergie von  $\sqrt{s} = 250 \text{ GeV}$  (Phinneya u. a., 2007).

| Parameter                          | Wert              | Einheit                          |

|------------------------------------|-------------------|----------------------------------|

| Schwerpunktsenergie                | 250               | GeV                              |

| Spitzen-Luminosität                | $2 \cdot 10^{34}$ | cm <sup>-2</sup> s <sup>-1</sup> |

| Pulsrate                           | 5                 | Hz                               |

| Pulslänge                          | 969               | μs                               |

| Anzahl der Teilchenpakete pro Puls | 2625              |                                  |

| Beschleunigungsfeldgradient        | 31,5              | MV/m                             |

| Teilchenpaket-Abstand              | 369               | ns                               |

| Teilchenpaket-Länge                | 300               | μm                               |

| Horizontale Strahlgröße            | 640               | nm                               |

| Vertikale Strahlgröße              | 5,7               | nm                               |

| Anzahl an Teilchen pro Paket       | $2 \cdot 10^{10}$ |                                  |

Beim ILC werden bei einer Schwerpunktsenergie von  $\sqrt{s}=500~{\rm GeV}$  innerhalb einer Paketgruppe rund 10 überwiegend durch Bhabha-Streuung verursachte Ereignisse in einem Vorwärtswinkelbereich von 30 mrad bis 90 mrad erwartet (Phinneya u. a., 2007). Damit muss mit Ereignisraten im Bereich von einigen kHz gerechnet werden. Obwohl die maximal zu erwartende Ereignisrate im Vergleich zu denen aktueller Hadronenbeschleuniger klein ist, können die Spitzenraten innerhalb einer Paketgruppe einige MHz erreichen (Behnke u. a., 2007).

<sup>&</sup>lt;sup>4</sup>engl. trains.

<sup>&</sup>lt;sup>5</sup>engl. bunch.

**Abbildung 1.2:** Struktureller Aufbau der Teilchenpakete, die im ILC beschleunigt und zur Kollision gebracht werden.

#### 1.1.2 Anforderung an die Detektoren für den ILC

Der International Linear Collider ermöglicht aufgrund des geringen Untergrunds bei der Elektron-Positron-Kollision und der wohlbekannten Schwerpunktsenergie höchst präzise Messungen. Die Prozesse zum Nachweis des Higgs-Teilchens, der Supersymmetrie oder die Bestimmung der Top-Quark-Eigenschaften und die Genauigkeit mit der diese gemessen werden sollen, geben die Anforderungen an die Detektoren für den ILC vor (Djouadi u. a., 2007). Um die angestrebte Präzision zu erreichen, müssen alle Detektorkomponenten deutliche Verbesserungen gegenüber bisher genutzten Systemen erfahren, so dass dies eine große Herausforderung bei der Entwicklung eines solchen Detektors darstellt.

Bedingt durch die Zeitstruktur der Teilchenpakete soll der gesamte Detektor nicht nach jedem einzelnen Ereignis ausgelesen werden, sondern kontinuierlich über die Zeitspanne einer Paketgruppe. Die Daten werden daher zwischengespeichert, in der Zeit zwischen zwei Paketgruppen verarbeitet und dauerhaft gesichert, sofern physikalisch interessante Ereignisse selektiert wurden. Diese kontinuierliche Auslese stellt zusätzlich neue Anforderungen an den Detektor, insbesondere an die Auslesegeschwindigkeit.

Um einen möglichst großen Raumwinkelbereich zu erfassen, umgeben die Messinstrumente des Detektors den Vertex in einer Schalenstruktur. Im Inneren wird ein Vertexdetektor zur präzisen Vermessung der Teilchenspuren angeordnet. Die Bestimmung der Vertices ist von essenzieller Bedeutung für eine genaue Messung der Reaktionen schwerer Teilchen. Die folgende Schicht bildet der Spurdetektor. Auch hier sollen die Teilchenspuren vermessen werden, allerdings sind aufgrund des größeren Abstands zum Strahlrohr die Anforderungen an die Strahlenresistenz und die absolute Auflösung geringer.

Mit Hilfe eines Magnetfeldes kann, wie in Abschnitt 1.2.2 erklärt wird, der transversale Impuls  $p_T$  der Teilchen bestimmt werden. Eine sehr hohe transversale Impulsauflösung ist notwendig, um die Higgs-Masse präzise messen zu können. Es wird dabei eine Impulsauflösung von

$$\delta(1/p_T) \le 5 \cdot 10^{-5} \cdot c \, \frac{1}{\text{GeV}}$$

(1.4)

angestrebt, welche um eine Größenordnung besser ist als die am LEP (Krautscheid, 2008).

An das Spurmesssystem schließt sich das elektromagnetische Kalorimeter, in dem die von Elektronen und Photonen deponierte Energie gemessen wird, an. Im folgenden hadronischen Kalorimeter wird mit ähnlichen Methoden die Energiedeposition von Hadronen vermessen. Durch Unterteilung der Kalorimeter in Segmente lassen sich außerdem Richtungsinformationen der Teilchen gewinnen. Die angestrebte Energieauflösung von

$$\frac{\sigma_E}{E} = \frac{0.3}{\sqrt{E/\text{GeV}}}\tag{1.5}$$

stellt eine um den Faktor zwei bessere Energieauflösung dar, als sie bei LEP erreicht wurde (Krautscheid, 2008; Ild, 2009). Das Teilchenflusskonzept<sup>6</sup> ermöglicht es, diese hohen Auflösungen zu erreichen. Beim Teilchenflusskonzept werden die Energien der geladenen Teilchen aus den Teilchenschauern schon im Spurdetektor gemessen und ersetzen damit die das herkömmliche Vorgehen, diese Energie in den Kalorimetern zu messen, da in den zu erwartenden Teilchenenergien die Spurauflösung der Kalorimeterauflösung überlegen ist. Nur die Energien der neutralen Teilchen werden in den Kalorimetern gemessen. Auf diese Weise kann eine Verbesserung der Energieauflösung des Teilchenschauers erzielt werden, wenn die Energiedepostion von geladenen und neutralen Teilchen im Kalorimeter eindeutig getrennt werden kann.

Umgeben werden die Detektorschichten von einem supraleitenden Magneten, dessen Feld in etwa 4 T betragen soll. Zur Erfassung von Myonen dienen Myonenkammern, welche in das Joch der Magnete eingelassen sind. Diese bilden die letzte Schicht des Detektors. Ergänzt wird das System durch Detektorkomponenten, die den Eintritt der Strahlrohre eng umschließen, um möglichst den gesamten Raumwinkel erfassen zu können.

Die Entwürfe für den ILC sehen vor, dass mit zwei Detektoren gegenseitig kontrollierende Experimente durchgeführt werden können. Zur Kostenreduktion sollen die Detektoren in einer Halle untergebracht und abwechselnd in den Strahl geschoben werden. Es wurden für den ILC vier Detektorkonzepte vorgeschlagen (Behnke u. a., 2007; Ild, 2009; Sid, 2009; 4th, 2009): Das *Large Detector Concept* (LDC), der *Global Large Detector* (GLD), das *Silicon Detector Concept* (sid) und der *Fourth Concept Detector* (4<sup>th</sup>). Die Konzepte LDC und GLD wurden aufgrund großer Ähnlichkeiten zum *International Large Detector* (ILD) zusammengefasst. Die einzelnen Konzepte unterscheiden sich vor allem in der Größe, dem Spurdetektor, dem konkreten Aufbau der Kalorimeter, sowie dem Magnetfeld. Außer dem SiD sehen alle Detektorkonzepte eine Zeitprojektionskammer als Möglichkeit für den zentralen Spurdetektor vor. Ebenso machen abgesehen vom 4<sup>th</sup> Konzept, welches auf hochauflösende kompensierende Kalorimeter setzt, alle Detektorkonzepte von dem Teilchenflussansatz Gebrauch (Schäfer, 2005; Stöver, 2007; Beck, 2008).

#### 1.2 Zeitprojektionskammern

Die Detektorentwürfe unterscheiden sich besonders in der Art der Spurmessung. Die Spurdetektoren bei zwei der Detektorkonzepte für den ILC basiert auf einer Zeitprojektionskammer (TPC)<sup>7</sup>, einem gasbasierten Konzept. Eine TPC stellt eine spezielle Form von einer Driftkammer dar und besteht zum größten Teil aus einem sensitiven Detektorvolumen, das mit Gas gefüllt ist. Im sensitiven Volumen

<sup>&</sup>lt;sup>6</sup>engl. particle flow.

<sup>&</sup>lt;sup>7</sup>engl. Time Projection Chamber.

werden geladene Teilchen erfasst, die durch elektromagnetische Wechselwirkung in der Lage sind, das Gas entlang ihrer Bahn zu ionisieren.

Da aber Driftelektronen in Gasdetektoren als Informationsträger dienen, unterliegt die Auflösung den Diffusionseffekten. Ebenso hängt die Auslesegeschwindigkeit stark von der Driftgeschwindigkeit in der Gasmischung ab. Obwohl Siliziumdetektoren schneller arbeiten und eine prinzipiell höhere Auflösung bieten, erschwert der Festkörper – begünstigt durch Vielfachstreuung – die präzise Vermessung langer Teilchenbahnen.

Gas als sensitives Medium hat den Vorteil, dass es kaum zu Wechselwirkungen mit den zu untersuchenden Teilchen kommt. Der Materialbedarf einer TPC ist extrem gering. Das eigentliche Nachweisvolumen ist bis auf das Zählgas nahezu materialfrei und minimiert die Mehrfachstreuung und Photonenkonversion (Ummenhofer, 2008). Durch Messung des Energieverlustes im Detektor kann eine Teilchenidentifikation durchgeführt werden.

#### 1.2.1 Wechselwirkung von Teilchen mit Materie

Die in der Hochenergiephysik betrachteten Teilchen verfügen in der Regel über Bewegungsenergien, die um mindestens sechs Größenordnungen oberhalb der Ionisationsenergien von Atomen und Molekülen liegen. Diese Teilchen können einen Teil ihrer kinetischen Energie durch Anregung von gebunden Elektronen oder Ionisation beim Durchgang durch Materie verlieren. Angeregte Atome können diese Energie in Form von niederenergetischen Photonen wieder abgeben. Ebenso ist der Energieverlust durch Streuprozesse in Gasdetektoren von großer Bedeutung. Dabei wird dem gebunden Elektron soviel Energie übertragen, dass es den Atomverband verlässt und ein Elektron-Ion-Paar bildet.

Der mittlere Energieverlust pro Wegstrecke dE/dx für schwere ( $m > m_e$ ) geladene Teilchen im Absorbermaterial durch Ionisation und Anregung wird durch die Bethe-Bloch-Formel beschrieben (Kleinknecht, 2005):

$$-\frac{dE}{dx} = \frac{4\pi}{m_e c^2} \cdot \frac{N_0 Z z^2}{A \beta^2} \cdot \left(\frac{e^2}{4\pi \varepsilon_0}\right)^2 \cdot \left[\ln\left(\frac{2m_e c^2 \beta^2}{I \cdot (1 - \beta^2)}\right) - \beta^2\right],\tag{1.6}$$

wobei  $N_0$  die Avogadro-Zahl, Z und A die Ordnungs- und Massenzahl des Materials, ze und  $v = \beta c$  die Ladung und Geschwindigkeit des bewegten Teilchens,  $m_{\rm e}$  die Ruhemasse des Elektrons,  $\varepsilon_0$  die Dielektrizitätskonstante und I das effektive Ionisationspotenzial des Materials sind.

Die Bethe-Bloch-Formel muss für geladene Teilchen mit  $m=m_{\rm e}$  modifiziert werden, da bei der Herleitung der Formel davon ausgegangen wird, dass die schweren Stoßpartner bei der Wechselwirkung mit den Elektronen des Absorbermaterials keine Ablenkung erfahren. Bei der Elektron-Elektron-Streuung muss zudem auch das Pauli-Prinzip beachtet werden. Die Bethe-Bloch-Formel muss dahingehend korrigiert werden. Die Energieverluste durch Bremsstrahlung müssen wegen der geringen Masse der Elektronen in Materie ebenfalls berücksichtigt werden. Dieser Beitrag ist für hohe Energien dominant.

Das geladene Teilchen, das die Kammer von Gaskammern durchquert, ionsiert pro Wegstrecke nur ein einzelnes Gasteilchen. Die mittlere freie Weglänge bis zum nächsten Stoß hängt vom Wirkungsquerschnitt des Teilchens in dem Gas ab. Man unterscheidet zwischen bei der Ionisation entstehenden Primär- und Sekundär-Elektronen. Primärelektronen werden von den die Kammer durchgehenden Teilchen durch Ionisation der Gasteilchen erzeugt. Die Sekundärelektronen stammen aus der Ionisation, die durch Stöße der Primärelektronen mit den Gasteilchen verursacht wurden. Diese entstehen

Abbildung 1.3: Funktionsweise einer Zeitprojektionskammer.

häufig sehr nah am Entstehungsort des Primärelektrons, so dass sich entlang der Teilchenspur Elektronenbündel<sup>8</sup> bilden. Einige wenige Primärelektronen, die so genannten  $\delta$ -Elektronen, verfügen über ausreichend Energie, um signifikant von ihrem Entstehungsort durch Ionisation entlang ihrer Bahn eine eigene Spur zu erzeugen (Krautscheid, 2008).

Neutrale Teilchen (beispielsweise Photonen) hinterlassen keine ionisierte Teilchenspur und sind deshalb für eine Spurkammer unsichtbar. Ungeladene Teilchen müssen ihre Energie auf geladene Teilchen übertragen, die ihrerseits Spuren im Detektorgas erzeugen. Bei Photonen geschieht dies über elektromagnetische Wechselwirkungen, wobei der Fotoeffekt, der Compton-Effekt und die Paarbildung auftreten können (Beck, 2008; Ummenhofer, 2008).

#### 1.2.2 Spurrekonstruktion durch Zeitprojektion

Eine Zeitprojektionskammer dient zur räumlichen Erfassung von Teilchenspuren. Der Detektor besteht im Wesentlichen aus einem großen gasgefüllten, zylindrischen Driftvolumen (Abbildung 1.3). Als Detektorzählgas wird in der Regel ein Edelgas verwendet. Edelgasatome sind einatomig, so dass keine Schwingungs- oder Rotationsfreiheitsgrade angeregt werden können und der Energieübertrag durch Ionisation überwiegt. Wenn ein ionisierendes Teilchen die Kammer passiert, verliert es Energie und hinterlässt eine Spur aus Elektronen-Ionenpaaren.

Der die Kammer umgebene Feldkäfig erzeugt ein homogenes elektrisches Feld in der Driftkammer. Elektronen aus der primären Ionisation driften daher in Richtung der Anoden und eine Rekombination der entstanden Ionen wird verhindert. Diese Primärelektronen der Ladungsspur gelangen auf die Gasverstärkungsstrukturen an der Anodenseite. Diese wiederum vervielfältigen die Anzahl der eintreffenden Elektronen so stark, dass genug Ladung für eine Auslese erzeugt wird. Die Auslese erfolgt dann mit auf der Stirnfläche befindlichen ladungsempfindlichen Detektoren.

Aus der Driftzeit der Elektronen im Driftvolumen lässt sich die dritte räumliche Komponente der Spur rekonstruieren. Zum Zeitpunkt  $t_0$  wird eine Zeitmessung gestartet, sobald das geladene Teilchen

<sup>8</sup>engl. cluster.

Abbildung 1.4: Elektronenmikroskopaufnahme eines GEMs: Löcher von rund 70  $\mu$ m Durchmesser werden im Abstand von rund 140  $\mu$ m in eine 50  $\mu$ m dicke Kapton-Schicht geätzt, die beidseitig mit 5  $\mu$ m Kupfer bedampft wurde (Ropelewski, 2009).

die Kammer durchquert und eine Spur aus Ladungsträgern hinterlässt. Zum Zeitpunkt  $t_1$  wird die Messung beendet, sobald die Ladungsspur in der Auslese erfasst wird. Wenn man annimmt, dass die Primärelektronen mit einer konstanten Geschwindigkeit  $v_{\text{Drift}}$  durch das Volumen driften, kann die Driftstrecke  $s_{\text{Drift}}$  durch  $s_{\text{Drift}} = v_{\text{Drift}} \cdot (t_1 - t_0)$  bestimmt werden. Die Umrechnung der Driftzeit in eine Driftstrecke erklärt auch den Namensursprung der Zeitprojektionskammer.

Zusätzlich zum elektrischen Feld kann noch ein dazu paralleles Magnetfeld B angelegt werden. Auf die den Detektor durchquerenden Teilchen wirkt somit die Lorentzkraft, so dass die Flugbahn durch eine Helix beschrieben wird. Aus der Messung des Krümmungsradius r lässt sich gemäß  $p_T = q \cdot B \cdot r$  der transversale Impuls  $p_T$  eines Teilchens mit der Ladung q bestimmen. Des Weiteren reduziert das Magnetfeld die transversale Diffusion der driftenden Elektronen und verbessert dadurch die Punktauflösung des Detektors (Krautscheid, 2008; Stöver, 2007; Ummenhofer, 2008).

#### 1.2.3 Gasverstärkung mit GEM-Stapeln

Primärelektronen können in einem elektrischen Feld so stark beschleunigt werden, dass diese wiederum genug Energie besitzen, um weitere Gasatome zu ionisieren. Ebenso können die Sekundärelektronen zur Erzeugung weiterer Ladungsträger beitragen. Bei genügend starken Feldgradienten kann dies zu einer lawinenartigen Vervielfältigung eines Elektronsignals führen. Ausschlaggebend für den Verstärkungsfaktor ist das lokal vorherrschende Feld und das verwendete Gas.

In Zusammenhang mit Zeitprojektionskammern werden alle Elektronen, die direkt oder indirekt beim Teilchendurchgang entstehen, als Primärelektronen bezeichnet. Als Sekundärelektronen bezeichnet man die Elektronen, die bei der Gasverstärkung entstehen.

Gaselektronenvervielfacher (GEM)<sup>9</sup> sind eine Methode zur Signalverstärkung in Zeitprojektionskammern. GEMs sind dünne Folien, die beidseitig mit einer Metallschicht bedampft sind und damit prin-

<sup>&</sup>lt;sup>9</sup>engl. Gas Electron Multiplier.

| <b>Tabelle 1.2:</b> Anforderungen an eine Zeitprojektionskammer für den <i>International Linear Collider</i> im Rahmen des |

|----------------------------------------------------------------------------------------------------------------------------|

| International Large Detector-Konzeptes (Ild, 2009).                                                                        |

| Detektor-Anforderung                | Wert                                                       |

|-------------------------------------|------------------------------------------------------------|

| Impulsauflösung (nur für die TPC)   | $\delta(1/p_T) \approx 9 \cdot 10^{-5} \cdot c/\text{GeV}$ |

| Impulsauflösung (gesamt)            | $\delta(1/p_T) \approx 2 \cdot 10^{-5} \cdot c/\text{GeV}$ |

| трс-Materialbudget                  | $0.04 X_0$ in $r$ -Richtung                                |

|                                     | $0,15 X_0$ in $z$ -Richtung                                |

| Anzahl der Kontaktflächen           | $1 \cdot 10^{6}$                                           |

| Einzelpunktauflösung in $r \varphi$ | < 100 μm                                                   |

| Einzelpunktauflösung in <i>rz</i>   | ≈ 0,5 mm                                                   |

| Doppelspurauflösung in $r arphi$    | ≈ 2 mm                                                     |

| Doppelspurauflösung in rz           | ≈ 6 mm                                                     |

| dE/dx Auflösung                     | ≈ 5 %                                                      |

zipiell einen Kondensator bilden. In diese Folie wird ein regelmäßiges Muster aus Löchern eingeätzt (Abbildung 1.4).

Zwischen der oberen und der unteren Elektrode wird eine Potentialdifferenz von einigen hundert Volt angelegt. In den GEM-Löchern bilden sich dadurch elektrische Felder von bis zu  $E=8.0\cdot10^6\,\frac{\rm V}{\rm m}$ . Um eine für den Detektor ausreichende Signalverstärkung zu gewährleisten, werden mehrere GEMS zu einem Stapel zusammengefasst. Dies ermöglicht eine Vervielfachung der Verstärkung um jeweils eine Größenordnung für jede zusätzliche GEM im Stapel (Ummenhofer, 2008).

Die Primärelektronen werden beim Driften zur Anode in den GEM-Löchern gesammelt. Durch das starke Feld werden in den Löchern aufgrund der Gasverstärkung Elektron-Ion-Paare erzeugt. Die vervielfachten Elektronen werden anschließend in das darunterliegende Gasvolumen extrahiert. Hier treffen sie auf weitere GEMS und werden weiter verstärkt. Am Ende wandern die vervielfachten Elektronen zur Ausleseebene und können dort von Detektoren erfasst werden.

Der Ausleseprozess bei GEMS ist gegenüber anderen Gasverstärkungssystemen wie Drahtkammern deutlich verkürzt. Das legt die Verwendung von GEMS für den Detektor des geplanten Linearbeschleunigers nahe. Die direkten Elektronensignale der GEMS sind schmaler als die Influenzsignale der Drahtkammern. Um dadurch zu einer besseren Auflösung zu kommen, wird allerdings auch eine feinere Strukturierung der Auslesefläche erforderlich (Ummenhofer, 2008).

#### 1.2.4 Anforderungen an die Zeitprojektionskammern für den ILC

Im Folgenden werden die Anforderungen an die TPC für den ILC vorgestellt, welche im Rahmen des ILD veröffentlicht wurden (Ild, 2009). Diese Anforderungen sind in der Tabelle 1.2 zusammengefasst. Danach wird die TPC für den ILC einen Außendurchmesser von 3,6 m und eine Gesamtlänge von 4,3 m besitzen. Die geforderte Impulsauflösung für das gesamte Spurdetektorsystem beim ILD soll

$$\delta(1/p_T) \approx 2 \cdot 10^{-5} \cdot c \, \frac{1}{\text{GeV}}$$

betragen. Dabei soll die Impulsauflösung nur der TPC

$$\delta(1/p_T) \approx 9 \cdot 10^{-5} \cdot c \, \frac{1}{\text{GeV}}$$

betragen. Zur Bestimmung der Krümmungsradien hochenergetischer Teilchen muss die TPC mit ausreichender Ortsauflösung messen. Wenn die angestrebte Ortsauflösung von 100  $\mu$ m in der  $r\varphi$ -Ebene und 500  $\mu$ m in z-Richtung erreicht werden soll, muss die Ladungsverteilung der ankommenden Elektronen sehr genau gemessen werden. Dazu existieren zwei Verfahren zur Auslese der TPC, die auf den zwei Endkappen, welche jeweils eine Fläche von rund  $10 \text{ m}^2$  besitzen werden, angebracht sind. Die eine Möglichkeit besteht mit einer konventionellen Auslese der Ladung über kleine elektronische Kontaktflächen  $^{10}$  der Größe von  $1 \text{ mm} \cdot 5 \text{ mm}$ . Ungefähr  $^{10}$  dieser Kontaktflächen würden sich auf einer Endkappe befinden. Bei dieser konventionellen Art der Auslese kann es zu einem Verlust an Präzision kommen, wenn die gesamte Ladung von nur einer Kontaktfläche gesammelt wird. Dies könnte mit einer Aufweitung des Signals nach der Gasverstärkung korrigiert werden (Krautscheid, 2008).

Eine Alternative zu der konventionellen Auslese bieten  $CMOS^{11}$ -Chips, welche eine sehr feine Segmentierung aufweisen und daher keine zusätzliche Verbreiterung des Signals erfordern. Diese Chips besitzen ladungsempfindliche Kontaktflächen in der Größe von rund 50  $\mu$ m. Das resultiert in einer Abdeckung der Endkappen mit rund 2  $\cdot 10^9$  Kontaktflächen, was einer Anzahl von rund 4  $\cdot 10^4$  Chips entspricht. Eine solche Auslese verspricht eine bisher unerreichte feine Segmentierung der Auslesefläche bei gleichzeitig minimalem Materialaufwand, da Teile der Ausleseelektronik in die Auslesefläche integriert werden können.

Insgesamt ist eine Minimierung des Materialaufwands unter anderem hinsichtlich der präzisen Energiemessung mittels des Teilchenflusskonzepts wichtig. Eine TPC hat hier den Vorteil, dass sie eine hohe Ortsauflösung bei einem minimalen Materialaufwand realisiert. Für die TPC am ILD ist ein Materialbudget von rund 0,01 Strahlungslängen für den inneren und 0,03 Strahlungslängen für den äußeren Feldkäfig von der Strahlachse radial nach außen vorgesehen. Zusätzlich resultieren 0,01 Strahlungslängen aus dem Gas. Die Endkappen, welche die Ausleseelektronik beinhalten, stellen das größte Hindernis für das durchgehende Teilchen dar. Hier besteht das Ziel, den Materialbedarf so weit zu minimieren, dass die Teilchen weniger als 0,15 Strahlungslänge durchqueren müssen.

Aus den nominalen Parametern des Beschleunigers in Tabelle 1.1 ergibt sich bei einer Kollision eine Rate von 2,6 MHz über 1 ms, gefolgt von 200 ms ohne jegliche Wechselwirkung. Daraus folgt eine Gesamt-Kollisionsrate von 13 kHz. Das Datenaufkommen am ILC wird von einem maschineninduzierten Untergrund dominiert werden. Die Hauptursache für den Untergrund sind alle Teilchen, welche ungewollt allein durch den Betrieb des Beschleunigers entstehen, vornehmlich Teilchen durch Paarbildung aus der unerwünschten Emission von Photonen, welche durch Ablenkung der geladenen Teilchen in den Paketen entsteht<sup>12</sup>. Aufgrund dieses Untergrunds erwartet man bei jeder Durchquerung der Teilchenpakete<sup>13</sup> in der TPC ungefähr 400 Treffer<sup>14</sup>. Physikalisch interessante Ereignisse tragen dagegen nur zu weniger als einem Prozent der aufgezeichneten Daten bei.

<sup>10</sup>engl. Pads.

<sup>&</sup>lt;sup>11</sup>Aus dem Englischen für Complementary Metal Oxide Semiconductor. CMOs bezeichnet sowohl die Kombination von p-Kanal- und n-Kanal-Metalloxid-Halbleiter-Feldeffekttransistor als auch eine Logikfamilie. Hier ist lediglich der Prozess zur Realisierung von integrierten Schaltungen gemeint.

<sup>&</sup>lt;sup>12</sup>Dieser Effekt wird im Englischen mit beamstrahlung bezeichnet.

<sup>13</sup> engl. bunch crossing.

<sup>14</sup>engl Hits.

## 2 TimePix-Chip

Die TPC für den ILC bietet eine gute Alternative für die präzise Rekonstruktion von Spuren geladener Teilchen. Das Ziel ist es daher, eine Technik zu entwickeln, welche die Auslese der TPC erlaubt, Informationen zum dreidimensionalen räumlichen Verlauf der Spur und zu der deponierten Ladung gibt. Zudem muss ein solches Auslesesystem die Anforderungen an die Orts- und Zeitauflösung, sowie die Ausleseraten erfüllen (Abschnitt 1.2.4).

Eine Möglichkeit zur Auslese der Signale nach der Gasverstärkung in einer Driftkammer sind anwendungsspezifische integrierte Schaltungen¹, welche ladungsempfindliche Elemente auf der Oberfläche besitzen. Aus der Röntgen- und Teilchenphysik ist der Medipix2-Detektor für seine bildgebenden Eigenschaften bekannt (Llopart u. a., 2002; Bamberger u. a., 2007). Der Medipix2-Detektor besteht aus dem Medipix2-Chip, dessen Kontaktflächen² über Lotkügelchen mit einem Halbleiterdetektor verbunden sind. Innerhalb des Chips ist jede Kontaktfläche mit einer Verstärkereinheit und Signalverarbeitungelektronik zur Auswertung der Ladungspulse, die im Halbleiterdetektor erzeugt werden, verbunden. Dadurch erlaubte der Medipix2-Chip eine Energiemessung und das Zählen einzelner Photonen (Korn, 2007; Jakubek u. a., 2008).

Speziell für die Auslese einer Zeitprojektionskammer wurde der TimePix-Chip auf Basis des Medipix2-Chips weiterentwickelt. Wird der TimePix-Chip ohne Halbleiterdetektor betrieben, liegen die Kontaktflächen frei und sind empfindlich für die Ladung (Abbildung 2.1). Im Gegensatz zum Medipix2-Chip kann der TimePix-Chip auch die Ankunftszeiten der Signale in der Zeitprojektionskammer bestimmen. Dies geschieht durch Abgleichen der Signale mit dem globalen Taktsignal des Chips.

Der TimePix-Chip ist ein in Standard-CMOS-Technologie³ gebauter ASIC. Im folgenden Kapitel wird der Aufbau des TimePix-Chips beschrieben. Ebenso wird die Verarbeitung der analogen Ladungssignale und deren Digitalisierung erklärt. Außerdem werden die vier Betriebsmodi des TimePix-Chips vorgestellt. Diese Modi ermöglichen durch ihre unterschiedliche Verarbeitungsweise der einkommenden Signale einen Einsatz des TimePix-Chips zur Driftzeit- und Ladungsmengenbestimmung sowie zum Zählen von Photonen. Daneben werden die Funktionen zur Steuerung und Bedienung des TimePix-Chips erläutert, welche zum Verständnis der nachfolgenden Kapitel, in denen die Entwicklung des Datenerfassungssystems für den TimePix-Chip beschrieben wird, notwendig sind.

#### 2.1 Aufbau des TimePix-Chips

Bei der Betrachtung des Aufbaus des TimePix-Chips in Abbildung 2.2 lässt sich eine schematische Aufteilung in zwei Bereiche erkennen. Der in der Abbildung 2.2 dargestellte untere Teil wird als Peripherie

<sup>&</sup>lt;sup>1</sup>engl. application specific integrated circuit, ASIC.

<sup>&</sup>lt;sup>2</sup>engl. bonding pad.

<sup>&</sup>lt;sup>3</sup>Prozess mit komplementären Metall-Oxid-Halbleitern (Englisch: Complementary Metal Oxide Semiconductor), die zur Realisierung von integrierten digitalen und analogen Schaltungen verwendet werden.

Abbildung 2.1: Der TimePix-ASIC mit der für die Auslese konzipierten Trägerplatine (Ummenhofer, 2008)

**Abbildung 2.2:** Schematischer Aufbau des TimePix-Chips. Die einzelnen Register in den Matrixzellen bilden eine 3584 bit breite Spalte. In Anlehnung an Llopart (2006).

Abbildung 2.3: Schematische Darstellung der Arbeitsweise der Matrixzellen

bezeichnet und beinhaltet die Ein- und Ausgabeeinheit. Hier findet die Verarbeitung der einkommenden und ausgehenden Signale statt, sowie die Kommunikation mit dem darüber liegenden Bereich. In der Peripherie befindet sich auch die Referenzspannungsquelle für die Digital-Analog-Umsetzer. Über die 127 Kontaktpunkte am unteren Rand der Peripherie wird eine leitende Verbindung zur Trägerplatine hergestellt. Dafür werden feine Drähte von wenigen 10 µm Durchmesser verwendet (Ummenhofer, 2008). In Abschnitt 2.4 wird noch ausführlicher auf die Funktionsweise der Peripherie eingegangen werden.

Der über der Peripherie befindliche Teil besteht aus einer ladungsempfindlichen Matrix aus  $256 \cdot 256$  quadratischen Matrixzellen, die jeweils eine Fläche von  $55 \, \mu m \cdot 55 \, \mu m$  besitzen. Die Matrix deckt somit eine Fläche von  $1,982 \, cm^2$  ab. Dies entspricht  $87 \, \%$  der Gesamtoberfläche von  $2,275 \, cm^2$  (Llopart, 2006; Llopart u. a., 2007). Jede Matrixzelle kann in einen analogen und einen digitalen Block unterteilt werden (Abbildung 2.3). Zuerst werden die Signale im analogen Block vorverstärkt und mit einer Schwellenspannung diskriminiert. Die Signale aus dem Diskriminator werden anschließend im digitalen Block weiterverarbeitet.

#### 2.2 Analoge Verarbeitung der Signale

Das Ziel der analogen Blocks in einer Matrixzelle ist die Verarbeitung der erfassten Ladungspulse. Die analoge Verarbeitung muss sicherstellen, dass nur solche Signale in eine für die Digitalisierung geeignete Form gebracht werden, welche für die Untersuchung entsprechende Mindest-Ladungsungsmengen besitzen. Dadurch soll verhindert werden, dass nur physikalisch interessante Signale und kein Rauschen detektiert werden.

Die passivierte Oberfläche einer jeden Matrixzelle ist dazu mit dem Eingang ihres Vorverstärkers verbunden. Jeder Vorverstärkereingang ist zudem über eine 8 fF Injektionskapazität an eine globale Injektionsleitung angeschlossen. Eine Transistorschaltung erlaubt es, diese Kapazität selektiv durch ein Testbit an- bzw. abzuschalten. Wie in Abschnitt 2.4.3 beschrieben wird, lässt sich somit durch Einkoppelung eines analogen Spannungspulses jede Matrixzelle individuell testen (Llopart, 2006; Ummenhofer, 2008).

Abbildung 2.4: Schema der analogen Sektion einer Matrixzelle in Anlehnung an Llopart (2006)

Der Vorverstärker erzeugt einen zur eingegangen Ladungsmenge proportionalen Spannungsimpuls. Dieser wird im Diskriminator mit konstanten Spannungsschwellen verglichen, woraufhin ein Ausgabesignal generiert wird. Die Dauer des Signals entspricht der Zeit des Eingangssignales über der Schwelle. Das Ausgabesignal wird anschließend im digitalen Block weiterverarbeitet (Abbildung 2.4).

#### 2.2.1 Vorverstärker

Die zentrale Baugruppe des Vorverstärkers ist ein Operationsverstärker, der über einen Kondensator gegengekoppelt ist. Diese Schaltung wirkt dann als Integrierer. Für die Ausgangsspannung  $U_a$  des Integrierers ergibt sich mit der Ladung Q und der Kapazität C die Integralgleichung

$$U_a = \frac{Q}{C} = \frac{1}{C} \cdot \left( \int_0^t I_c(\tau) d\tau + Q_0 \right). \tag{2.1}$$

Dabei ist  $Q_0$  die Ladung, die sich zu Zeit t = 0 bereits im Kondensator befindet und  $I_c$  der Strom durch den Kondensator.

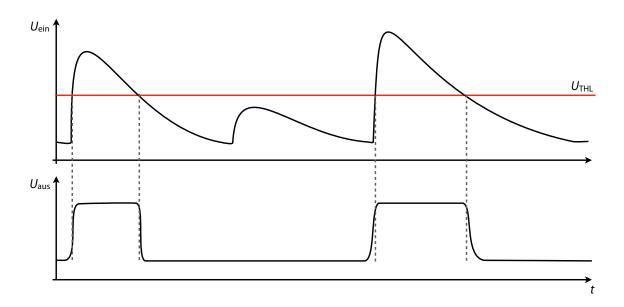

Gelangt nun eine Ladung Q an den Eingang des Vorverstärkers, wird diese zunächst im Kondensator gesammelt. Die aus der Integration resultierende Spannung wird dann am Ausgang des Vorverstärkers als Signal ausgegeben. Dieses Spannungssignal  $U_{\rm ein}$ , dessen Verlauf in der oberen Abbildung 2.5 exemplarisch dargestellt ist, entspricht einem asymmetrischen Dreieckssignal aufgrund der kurzen ansteigenden Flanke und der langgestreckten abfallenden Flanke.

Da der TimePix-Chip auch an Halbleiterdetektoren betrieben werden kann, muss die Vorverstärkerschaltung in der Lage sein, in Halbleiterdetektoren auftretende Leckströme zu kompensieren. Diese Kompensation wird durch eine Krummenacher-Schaltung gelöst (Krummenacher, 1991).

#### 2.2.2 Diskriminator

Der Diskriminator bildet die Vorstufe für die Digitalisierung. Die Spannung vom Vorverstärker  $U_{\rm ein}$  wird mit einer Schwellenspannung  $U_{\rm THL}$  verglichen und ein für die digitale Weiterverarbeitung geeignetes Signal erzeugt. Dabei wird ein Ausgangsspannungsimpuls erzeugt sobald der Spannungsimpuls vom Vorverstärker ein gewähltes Schwellenspannungsniveau überschreitet. Der Diskriminator ähnelt

**Abbildung 2.5:** Schematische Darstellung der Signalverarbeitung im Diskriminator. Oben dargestellt ist das vom Vorverstärker ausgegebene Signal  $U_{\rm ein}$ , welches die Form eines asymmetrischen Dreiecks besitzt. Unten ist das Diskriminator-Ausgangssignal  $U_{\rm aus}$  dargestellt.

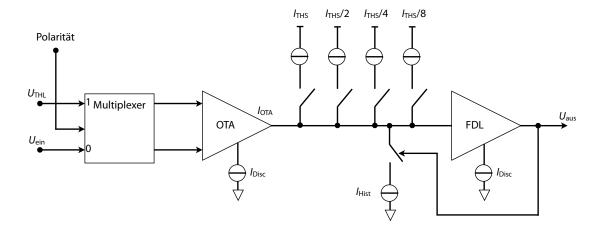

damit in seiner Funktion im Wesentlichen einem Komparator, in dem ebenfalls zwei Spannungen verglichen werden und ein Ausgangssignal erzeugt wird, welches zwei Zustände annehmen kann. In Abbildung 2.6 ist die Funktionsweise des Diskriminators in einem Blockschaltbild dargestellt.

Da der TimePix-Chip sowohl für negative als auch für positive Ladungen empfindlich ist, kann die Verstärkerspannung  $U_{\rm ein}$  sowohl negative als auch positive Polarität besitzen. Je nach zu erwartender Polarität wird vor einer Datennahme ein Steuersignal an den Multiplexer gelegt. Der Multiplexer stellt sicher, dass die nachfolgende Hysterese-Schaltung<sup>4</sup> unabhängig von der Eingangsladung arbeitet (Llopart u. a., 2007).

Anschließend werden die beiden Spannungen an den Transkonduktanz-Operationsverstärker (OTA)<sup>5</sup> mit der Transkonduktanz  $g_m$  angelegt. Der Ausgangsstrom  $I_{\rm OTA}$  wird durch die Spannungsdifferenz am Eingang gesteuert:

$$I_{\text{OTA}} = (U_{\text{THL}} - U_{\text{ein}}) \cdot g_m. \tag{2.2}$$

Der Strom ist somit negativ, falls die Verstärkerspannung größer ist als die Schwellenspannung. Er ist positiv, falls die Verstärkerspannung kleiner ist als die Schwellenspannung<sup>6</sup>.

Der Ausgangsstrom des Transkonduktanz-Operationsverstäkers wird dann in die schnelle Unterscheidungslogikschaltung (FDL)<sup>7</sup> geführt. Die FDL-Schaltung ändert ihre Ausgangsspannung, sobald

<sup>&</sup>lt;sup>4</sup>Eine Hysterese ist unter anderem eingebaut, um schnelle Wiederholungen von Ein- und Ausschaltvorgängen zu vermeiden. Siehe auch Llopart (2006).

<sup>&</sup>lt;sup>5</sup>engl. Operational Transconductance Amplifier.

$<sup>^6</sup>$ Durch den vorgeschalteten Multiplexer werden die Eingänge an den ота entsprechend vertauscht, so dass das Vorzeichen der Differenz  $U_{\text{THL}} - U_{\text{ein}}$  erhalten bleibt (Llopart, 2006).

<sup>&</sup>lt;sup>7</sup>engl. Fast Discriminator Logic.

**Abbildung 2.6:** Blockschaltbild des Diskriminators. Die Ströme  $I_{\text{Disc}}$  dienen zur Versorgung der Operationsverstärker im Diskriminator. Der Strom  $I_{\text{Hist}}$  steuert die Hysterese des Diskriminators. Dies garantiert das Zurückspringen des Diskriminatorsignals auf die logische Null, falls der Eingang durch ein ansteigendes Signal (z.B. Rauschen) überlagert sein sollte. In Anlehnung an Llopart (2006).

sich die Polarität von  $I_{\text{OTA}}$  an ihrem Eingang ändert. Dies geschieht, wenn das Vorverstärkersignal über die Schwelle steigt oder unter sie fällt und somit die Differenz ( $U_{\text{THL}} - U_{\text{ein}}$ ) = 0 ergibt.

An den FDL Eingang können vier zusätzliche Stromquellen  $I_{\rm THS}$ ,  $I_{\rm THS}/2$ ,  $I_{\rm THS}/4$  und  $I_{\rm THS}/8$  angeschlossen werden. Diese können unabhängig voneinander mittels vier Schaltbits über Transistoren hinzugefügt werden. Dadurch wird der Zeitpunkt, wann der Verlauf des Stroms  $I_{\rm OTA}$  einen Nulldurchgang besitzt, verändert. Diese Verschiebung des Arbeitspunkts des FDL ermöglicht eine Feinjustierung der effektiven Schwellen in jeder Matrixzelle.

Die minimale detektierbare Ladung ist definiert als die kleinste Ladungseinheit, welche alle Matrixzellen auflösen können, wenn die Schwellenspannung knapp über der Rauschschwelle eingestellt ist. Die minimale detektierbare Ladung entspricht für die gesamte Matrix ungefähr 1600 Elementarladungen. Nach einer Feinjustierung der effektiven Schwelle in jeder Matrixzelle beträgt die minimale detektierbare Ladung ungefähr 650 Elementarladungen (Llopart u. a., 2007).

#### 2.3 Digitale Verarbeitung der Signale

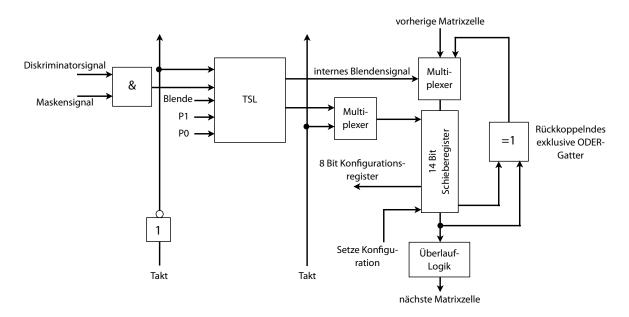

Das Ausgangssignal des Diskriminators wechselt nun lediglich zwischen zwei Spannungswerten. Somit kann dieses Signal für eine digitale Weiterverarbeitung mit Logikgattern verwendet werden. Die digitale Verarbeitung des Diskriminatorsignals in jeder Matrixzelle dient dazu, die Informationen aus diesem Signal dem Datenerfassungssystem leicht zugänglich zu machen. In Abbildung 2.7 ist der schematische Aufbau des digitalen Blocks einer Matrixzelle dargestellt.

Das Diskriminatorsignal und ein externes Maskensignal werden an ein und-Gatter angeschlossen. Wird das Maskensignal auf logisch Null gesetzt, wird das Diskriminatorsignal vom digitalen Block getrennt. Dadurch lässt sich das Zählen in einzelnen Matrixzellen individuell an- und ausschalten.

Der Ausgang des und-Gatters wird an die TimePix-Synchronisationslogikschaltung (TSL) weiterge-

Abbildung 2.7: Schema der digitalen Sektion einer Matrixzelle in Anlehnung an Llopart (2006)

leitet. An dieses wird zusätzlich ein externes Blendensignal<sup>8</sup>, je zwei Konfigurationssignale P0 und P1 und ein globales Taktsignal angelegt. Die maximale Taktfrequenz  $v_{\rm Takt}$ , mit der der TimePix-Chip betrieben werden kann, beträgt  $v_{\rm Takt} = 100$  MHz (Llopart, 2006; Llopart u. a., 2007). Die Information am Ausgang der TSL wird anschließend in ein 14 bit breites Schieberegister weitergeleitet.

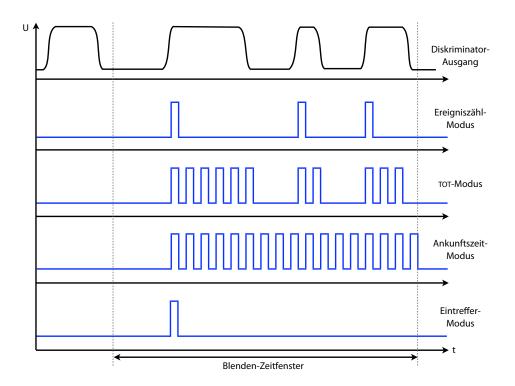

#### 2.3.1 TimePix-Synchronisationslogikschaltung

In Abhängigkeit von den beiden Konfigurationssignalen *P*0 und *P*1 synchronisiert die TSL das ungefähr rechteckförmige Signal vom Diskriminator und das Blendensignal mit dem Taktsignal (Abbildung 2.8). Die Verarbeitung in der TSL findet erst statt, wenn das Diskriminatorsignal auf einem hohen Pegel liegt und durch das Blendensignal ein definiertes Zeitfenster geöffnet wird. Das Blendensignal muss dafür auf einem niedrigen Pegel (logisch Null) liegen. Erst dann wird das interne Schieberegister der Matrixzelle je nach eingestellten Konfigurationssignalen mit dem Takt inkrementiert<sup>9</sup>. Das Blendensignal wird bei einer logischen Eins nicht gesetzt<sup>10</sup> (negative Logik).

Der TimePix-Chip kann in vier verschiedenen Betriebsmodi betrieben werden:

**Ereigniszähl-Modus:** In diesem Modus wird der Zählstand des Schieberegisters jedes Mal um Eins erhöht, wenn das Diskriminatorsignal auf einen hohen Pegel wechselt. Während die Blende geöffnet ist, wird in diesem Modus die Anzahl der Ladungspulse gemessen. Beim Betrieb mit einem Halbleiterdetektor kann somit auf die Photonenzählrate geschlossen werden.

<sup>&</sup>lt;sup>8</sup>engl. Shutter.

<sup>&</sup>lt;sup>9</sup>Zur Vereinfachung wird im Folgenden dieser Zustand als Öffnen der Blende bezeichnet.

<sup>&</sup>lt;sup>10</sup>Dieser Zustand wird im Folgenden als Schließen der Blende bezeichnet.

**Abbildung 2.8:** Funktionsprinzip der Signalverarbeitung des Diskriminatorsignals durch die vier Betriebsmodi der TSL in Anlehnung an Ummenhofer (2008)

TOT-Modus: Die TSL inkrementiert den Zähler für die Dauer, während der sich das Diskriminatorsignal auf einem hohen Pegel befindet<sup>11</sup>. Aus dem Zählstand und der Taktfrequenz lässt sich ein Zeitwert bestimmen. In diesem Modus wird die Zeitdauer, während der das Verstärkersignal bei geöffneter Blende über der Schwelle lag, gemessen. Die Zeitdauer ist proportional zu der Höhe der Eingangspulses und damit der deponierten Ladungsmenge pro Matrixzelle (Ummenhofer, 2008).

**Eintreffer-Modus:** In der Zeit, während der die Blende geöffnet ist, erhöht das erste Verstärkersignal über der Schwelle das Schieberegister um Eins. Jedes weitere Signal in diesem Zeitfenster wird ignoriert.

Ankunftszeit-Modus: Sobald der Pegel des Diskriminatorsignals zum ersten Mal zur logischen Eins innerhalb der geöffneten Blende wechselt, inkrementiert die TSL das Schieberegister mit dem Takt. Das Zählen wird erst durch das Ende des Blendensignals gestoppt. Aus der Kenntnis der Taktfrequenz kann damit eine Zeitmessung vorgenommen werden. In Referenz zum externen Blendensignal mit definierter Länge kann so die Ankunftszeit des Pulses ermittelt werden. Bei der maximalen Betriebsfrequenz  $v_{\text{Takt}} = 100 \text{ MHz}$  ergibt sich damit eine Zeitauflösung von 10 ns.

Die beiden Konfigurationssignale P0 und P1 versetzen jede Matrixzelle in einen von vier Betriebsmodi. In der Tabelle 2.1 sind die vier Modi aufgelistet, die durch Setzen der Konfigurationssignale P0 und P1 bestimmt werden.

<sup>&</sup>lt;sup>11</sup>Tot ist die englische Abkürzung für Time Over Threshold und bezeichnet die Zeitdauer über der Schwelle.

Tabelle 2.1: Die vier Betriebsmodi einer Matrixzelle

| P1 | P0 | Betriebsmodus      |

|----|----|--------------------|

| 0  | 0  | Ereigniszähl-Modus |

| 0  | 1  | тот-Modus          |

| 1  | 0  | Eintreffer-Modus   |

| 1  | 1  | Ankunftszeit-Modus |

#### 2.3.2 Funktion des Schieberegisters einer Matrixzelle

Das 14 bit breite Schieberegister einer jeden Matrixzelle arbeitet in Abhängigkeit vom Blendensignal auf zwei verschiedene Betriebsarten (Llopart u. a., 2007). Ist das Blendensignal nicht aktiv, kann man das 14-Bit-Register setzen und auslesen (Abschnitt 2.4.2). In dem Register werden 8 Konfigurationswerte einer Matrixzelle festgelegt. Damit lassen sich die vier Stromquellen  $I_{\rm THS}$ ,  $I_{\rm THS}/2$ ,  $I_{\rm THS}/4$  und  $I_{\rm THS}/8$  im Diskriminator zuschalten. Der Wert der Konfigurationssignale P0 und P1 kann gesetzt werden. Außerdem können das Testbitsignal und das Maskensignal an- und abgeschaltet werden.

Ist das Blendensignal aktiv, wird das Schieberegister zum linear rückgekoppelten Schieberegister und dient als Zähler für die TSL. Die Ausgänge des höchstwertigen Bits<sup>12</sup> und des niedrigstwertigen Bits<sup>13</sup> werden dabei über ein Exklusiv-ODER-Gatter an den Eingang des niedrigstwertigen Bits rückgekoppelt. Der maximale Zählstand kann mit dieser Technik 11810 betragen<sup>14</sup>.

#### 2.4 Steuerung des TimePix-Chips über die Ein- und Ausgabeeinheit

Zur Bedienung des TimePix-Chips mit einem Datenerfassungssystem ist die Kenntnis über sein Steuerprotokoll notwendig. Dieses wird in diesem Abschnitt beschrieben.

Alle Ein- und Ausgabeoperationen, die den Chip steuern, sowie die Register der Matrix setzen und auslesen, finden in der Peripherie statt. Der schematische Aufbau der Peripherie ist in Abbildung 2.9 dargestellt. Das Einlesen der Daten in den Chip bzw. das Auslesen der Daten kann entweder über die CMOS-Ein-/Ausgabelogikschaltung oder über die beiden LVDS-Treiber<sup>15</sup> erfolgen.

Über die CMOS-Ein-/Ausgabelogikschaltung werden hauptsächlich Signale eingelesen, die sich auf den ganzen Chip auswirken oder die ein schnelles Umschalten im Chip bewirken sollen. Auf diese Weise werden unter anderem das Blendensignal, die Polarität oder das Signal zum Zurücksetzen<sup>16</sup> des Chips in den Anfangszustand übertragen.

Über die LVDS-Treiber können serielle Datenströme ein- bzw. ausgelesen werden. Die Datenströme werden in ein 256 bit breites schnelles Schieberegister (FSR)<sup>17</sup> eingelesen. Die 14-Bit-Schieberegister der Matrixzellen können nun über das FSR angesteuert werden. Zu diesem Zweck werden die

<sup>&</sup>lt;sup>12</sup>engl. most significant bit (мѕв).

<sup>&</sup>lt;sup>13</sup>engl. least significant bit (LSB).

<sup>&</sup>lt;sup>14</sup>Das entspricht der maximalen Periodenlänge. Würde der Vorgang vorgesetzt werden, wäre der Inhalt identisch mit dem Inhalt im Ausgangszustand und die Zählwerte wären nicht mehr eindeutig. Siehe auch Llopart (2006).

<sup>&</sup>lt;sup>15</sup>engl. Abkürzung für Low Voltage Differential Signaling. LVDS beschreibt eine standardisierte Schnittstellen für eine Hochgeschwindigkeitsdatenübertragung.

<sup>16</sup>engl. Reset.

<sup>&</sup>lt;sup>17</sup>engl. Fast Shift Register.

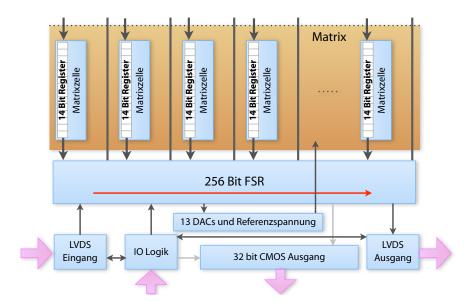

Abbildung 2.9: Schematische Darstellung der Peripherie des TimePix-Chips in Anlehnung an Llopart (2006)

14-Bit-Register benachbarter Matrixzellen in einer Matrixspalte über Multiplexer zu einem einzigen 256 · 14 bit = 3584 bit breiten Schieberegister verschaltet (Abbildungen 2.2 und 2.7). Die Daten aus dem FSR werden somit spaltenweise in die Schieberegister der Matrix geschrieben. Vice versa verläuft das Auslesen der Daten: Jedes Spaltenregisters schiebt bitweise seinen Inhalt in das FSR. Dabei erhält das 256 bit breite FSR parallel von allen 256 Spaltenregistern seinen Inhalt. Nach 256 Taktzyklen ist der Inhalt des FSR ausgelesen und der Prozess, dass alle 256 Spaltenregister je ein Bit ihres Inhalts in das FSR schieben, wird wiederholt, bis die gesamte Matrix ausgelesen ist. Auf diese Weise lassen sich die Strom- und Spannungsquellen des Chips steuern oder die Matrix ein- bzw. auslesen.

Damit die Interpretation der FSR-Daten richtig erfolgt, gibt es zusätzlich zwei смоs-Steuerleitungen (*M*0 und *M*1), die den Chip in die verschiedenen Betriebszustände versetzen (Tabelle 2.2).

| <i>M</i> 0 | <i>M</i> 1 | Operation                             |

|------------|------------|---------------------------------------|

| 0          | 0          | Auslesen der Matrix                   |

| 0          | 1          | Setzen der Matrix                     |

| 1          | 0          | Steuerung der Strom-/Spannungsquellen |

| 1          | 1          | Zählmodus                             |

Tabelle 2.2: Die Betriebszustände des TimePix-Chips

Die Matrix-Auslese ist auch über den 32 bit breiten CMOS-Ausgang möglich. Für eine Hochgeschwindigkeitsdatenübertragung ist aber die serielle Auslese mittels LVDS vorzuziehen. LVDS arbeitet mit geringeren Spannungspegeln als CMOS, weswegen die Verlustleistung durch Abstrahlung von elektromagnetischer Strahlung, bedingt durch die auftretenden schnellen Spannungsänderungen, minimiert wird. Durch die differentielle Signalführung wird zudem die Störempfindlichkeit reduziert (Nat, 2008; Huq u. Goldie, 1998).

#### 2.4.1 Steuerung der Strom- und Spannungsquellen des TimePix-Chips

Wie anfangs erwähnt, geschieht die globale Kontrolle der Strom- und Spannungsquellen des Chips über das 256 bit breite FSR. Dieses dient der Steuerung von 13 Digital-Analog-Umsetzern (DAC)<sup>18</sup>. Je acht von ihnen steuern Stromquellen, die restlichen fünf DACs steuern Spannungsquellen. Diese dienen zur globalen Einstellung der Arbeitspunkte der Vorverstärker und Diskriminatoren in den Matrixzellen. Unter anderem werden auf diese Weise auch die globale Schwellenspannung  $U_{\rm THL}$  und der individuelle Schwellenkorrekturstrom  $I_{\rm THS}$  gesetzt.

Die analoge Ausgabespannung jedes einzelnen der 13 Digital-Analog-Umsetzer kann ausgelesen und kontrolliert werden. Mit einem 4 bit langen Identifikationswert, der ins FSR geschrieben wird, kann ein einzelner DAC angesprochen werden. Durch Setzen eines Steuerbits im FSR kann die Spannung des DACS an dem Signalausgang des TimePix-Chips freigegeben werden.

Falls die globalen Parameter des Chips neu gesetzt werden, muss dafür das FSR neu beschrieben werden. Für das Beschreiben bzw. Auslesen des FSRs werden 256 + 8 Taktzyklen benötigt. Die zusätzlichen 8 Taktzyklen sind aufgrund eines angeschlossenen 8 bit langen Registers notwendig.

Wurde der Chip in den Anfangszustand zurückgesetzt, wird der Inhalt eines statischen 24-Bit-Registers, das die Identifikationsnummer des Chips enthält, in das FSR geschrieben. Beim anschließenden Setzen des FSR kann diese Identifikationsnummer simultan ausgelesen werden.

#### 2.4.2 Lese- und Schreiboperationen der Matrix

Beim Setzen der Matrix wird das 14-Bit-Schieberegister jeder Matrixzelle beschrieben. Dadurch können die 8 Konfigurationswerte eingestellt werden (Abschnitt 2.3.2). Die verbleibenden 6 Bits des Schieberegisters müssen ebenfalls beschrieben werden, erfüllen aber keine Steuerfunktion.

Beim Auslesen der Matrix wird der Inhalt des 14 bit breiten Schieberegisters jeder Matrixzelle übertragen. Wurde vor der Operation die Blende geöffnet, kann somit der Zählstand des linear rückgekoppelten Schieberegisters ausgelesen werden. War die Blende zwischen Auslese und Setzen der Matrix nicht geöffnet, wird einfach der Inhalt des Schieberegisters ausgegeben. Die Kommunikation mit dem TimePix-Chip funktioniert korrekt, wenn der ausgegebene Inhalt und die zuvor gesetzten Werte identisch sind.

Nach jedem Auslesen der Matrix werden die Schieberegister mit Einsen gefüllt. Daher sollte vor jedem Zählmodus die Matrix ausgelesen werden, damit alle Schieberegister sich in einem definierten Ausgangszustand befinden.