# Virtex-II Platform FPGA User Guide

UG002 (v1.6.1) 1 August 2003

"Xilinx" and the Xilinx logo shown above are registered trademarks of Xilinx, Inc. Any rights not expressly granted herein are reserved. CoolRunner, RocketChips, Rocket IP, Spartan, StateBENCH, StateCAD, Virtex, XACT, XC2064, XC3090, XC4005, and XC5210 are registered trademarks of Xilinx, Inc.

The shadow X shown above is a trademark of Xilinx, Inc.

ACE Controller, ACE Flash, A.K.A. Speed, Alliance Series, AllianceCORE, Bencher, ChipScope, Configurable Logic Cell, CORE Generator, CoreLINX, Dual Block, EZTag, Fast CLK, Fast CONNECT, Fast FLASH, FastMap, Fast Zero Power, Foundation, Gigabit Speeds...and Beyond!, HardWire, HDL Bencher, IRL, J Drive, JBits, LCA, LogiBLOX, Logic Cell, LogiCORE, LogicProfessor, MicroBlaze, MicroVia, MultiLINX, NanoBlaze, PicoBlaze, PLUSASM, PowerGuide, PowerMaze, QPro, Real-PCI, RocketIO, SelectIO, SelectRAM, SelectRAM+, Silicon Xpresso, Smartguide, Smart-IP, SmartSearch, SMARTswitch, System ACE, Testbench In A Minute, TrueMap, UIM, VectorMaze, VersaBlock, VersaRing, Virtex-II Pro, Virtex-II EasyPath, Wave Table, WebFITTER, WebPACK, WebPOWERED, XABEL, XACT-Floorplanner, XACT-Performance, XACTstep Advanced, XACTstep Foundry, XAM, XAPP, X-BLOX +, XC designated products, XChecker, XDM, XEPLD, Xilinx Foundation Series, Xilinx XDTV, Xinfo, XSI, XtremeDSP and ZERO+ are trademarks of Xilinx, Inc.

The Programmable Logic Company is a service mark of Xilinx, Inc.

All other trademarks are the property of their respective owners.

Xilinx, Inc. does not assume any liability arising out of the application or use of any product described or shown herein; nor does it convey any license under its patents, copyrights, or maskwork rights or any rights of others. Xilinx, Inc. reserves the right to make changes, at any time, in order to improve reliability, function or design and to supply the best product possible. Xilinx, Inc. will not assume responsibility for the use of any circuitry described herein other than circuitry entirely embodied in its products. Xilinx provides any design, code, or information shown or described herein "as is." By providing the design, code, or information as one possible implementation of a feature, application, or standard, Xilinx makes no representation that such implementation. Xilinx expressly disclaims any warranty whatsoever with responsible for obtaining any rights you may require for your implementation. Xilinx expressly disclaims any warranty whatsoever with respect to the adequacy of any such implementation, including but not limited to any warranties or representations that the implementation is free from claims of infringement, as well as any implied warranties of merchantability or fitness for a particular purpose. Xilinx, Inc. devices and products are protected under U.S. Patents. Other U.S. and foreign patents pending. Xilinx, Inc. does not represent that devices shown or products described herein are free from patent infringement or from any other third party right. Xilinx, Inc. assumes any bilability for the accuracy or correctness of any engineering or software support or assistance provided to a user.

Xilinx products are not intended for use in life support appliances, devices, or systems. Use of a Xilinx product in such applications without the written consent of the appropriate Xilinx officer is prohibited.

The contents of this manual are owned and copyrighted by Xilinx. Copyright 1994-2003 Xilinx, Inc. All Rights Reserved. Except as stated herein, none of the material may be copied, reproduced, distributed, republished, downloaded, displayed, posted, or transmitted in any form or by any means including, but not limited to, electronic, mechanical, photocopying, recording, or otherwise, without the prior written consent of Xilinx. Any unauthorized use of any material contained in this manual may violate copyright laws, trademark laws, the laws of privacy and publicity, and communications regulations and statutes.

#### Virtex<sup>™</sup>-II Platform FPGA User Guide UG002 (v1.6.1) 1 August 2003

The following table summarizes changes made to each version of this document. Publication versions are electronic only (PDF) unless otherwise stated.

| Date     | Version | Revision                                                                                                                                           |  |  |  |

|----------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 12/06/00 | 1.0     | (Printed version with data sheet modules 1-3 in Part I) Initial Release.                                                                           |  |  |  |

| 04/02/01 | 1.1     | Misc updates throughout.                                                                                                                           |  |  |  |

| 10/12/01 | 1.2     | Misc technical edits throughout.                                                                                                                   |  |  |  |

| 12/03/01 | 1.3     | (Printed version with data sheet modules 1-3 in Part I) Misc updates throughout.                                                                   |  |  |  |

| 11/01/02 | 1.4     | Misc updates throughout.                                                                                                                           |  |  |  |

| 12/02/02 | 1.5     | Misc updates throughout.                                                                                                                           |  |  |  |

| 04/21/03 | 1.6     | • Added HDL code for resetting the DCM after configuration in section "External Feedback" on page 71.                                              |  |  |  |

|          |         | Corrected Location Constraints syntax, multiple instances.                                                                                         |  |  |  |

|          |         | • Added LVDS_25 and LVDSEXT_25 to list of I/O standards that support DCI in section "DCI in Virtex-II Hardware" on page 200.                       |  |  |  |

|          |         | • Corrected and updated section "Using LVPECL I/O" on page 225.                                                                                    |  |  |  |

|          |         | • Corrected command-line equivalent statements for bitstream encryption key files in section "Creating Keys" on page 230.                          |  |  |  |

|          |         | Added new section "Abort" on page 268 to section Master SelectMAP Programming<br>Mode.                                                             |  |  |  |

|          |         | <ul> <li>Added LVDS_25 and LVDSEXT_25 to list of I/O standards that support DCI in<br/>section "DCI in Virtex-II Hardware" on page 200.</li> </ul> |  |  |  |

|          |         | • Revised description of the JTAG output in section "Test Access Port" on page 275.                                                                |  |  |  |

|          |         | • Updated configuration parameters in Table 3-16 on page 293.                                                                                      |  |  |  |

| 08/01/03 | 1.6.1   | Table 3-4 on page 255: Corrected bias voltage on dedicated pins from 2.5V to 3.3V. Other minor edits to this table and the text above it.          |  |  |  |

Virtex-II Platform FPGA User Guide

# Contents

### **About This Guide**

| Additional Resources      | . 9 |

|---------------------------|-----|

| Typographical Conventions | 10  |

### Introduction to the Virtex-II FPGA Family

| Virtex-II Platform                                                   | 11 |

|----------------------------------------------------------------------|----|

| Virtex-II Target Applications                                        | 11 |

| Interconnect Engine for Fast, Wide Busses in Networking Applications | 12 |

| Complete Solution For Rapid Time-to-Production                       | 12 |

# **Chapter 1: Timing Models**

| Summary                            | 13 |

|------------------------------------|----|

| CLB / Slice Timing Model           | 14 |

| Block SelectRAM Timing Model       | 23 |

| Embedded Multiplier Timing Model   | 26 |

| IOB Timing Model                   | 28 |

| Pin-to-Pin Timing Model            | 38 |

| Digital Clock Manager Timing Model | 42 |

# **Chapter 2: Design Considerations**

| Summary                                        | 47  |

|------------------------------------------------|-----|

| Introduction                                   | 47  |

| Using Global Clock Networks                    | 48  |

| Using Digital Clock Managers (DCMs)            | 67  |

| Using Block SelectRAM <sup>TM</sup> Memory     |     |

| Using Distributed SelectRAM Memory             | 115 |

| Using Look-Up Tables as Shift Registers (SRLs) | 125 |

| Designing Large Multiplexers                   | 135 |

| Implementing Sum of Products (SOP) Logic       | 145 |

| Using Embedded Multipliers                     | 152 |

| Using Single-Ended SelectI/O-Ultra Resources   | 159 |

| Using Digitally Controlled Impedance (DCI)     | 190 |

| Using Double-Data-Rate (DDR) I/O               | 206 |

| Using LVDS I/O                                 | 220 |

| Using LVPECL I/O                               | 225 |

| Using Bitstream Encryption                     | 229 |

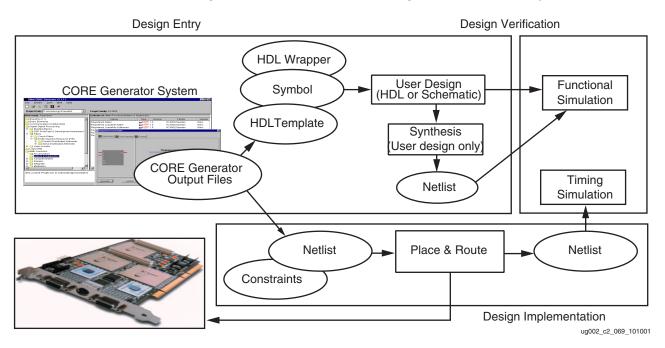

| LINX <sup>®</sup><br>Using the CORE Generator System | 233 |

|------------------------------------------------------|-----|

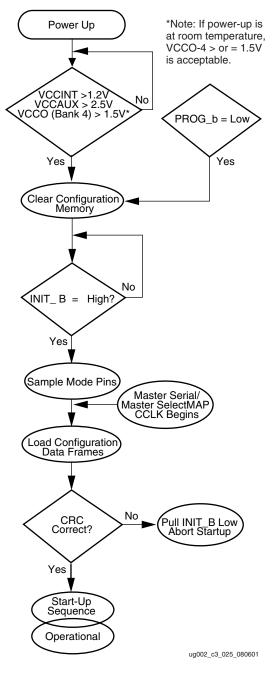

| Chapter 3: Configuration                             |     |

| Summary                                              | 249 |

| Introduction                                         | 249 |

| Configuration Solutions                              | 257 |

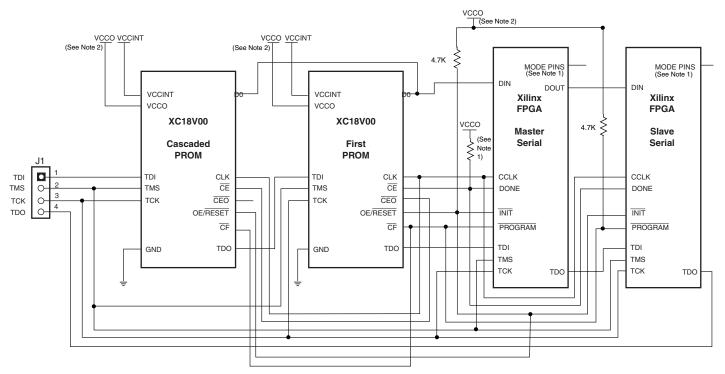

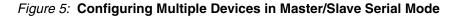

| Master Serial Programming Mode                       | 264 |

| Slave Serial Programming Mode                        | 265 |

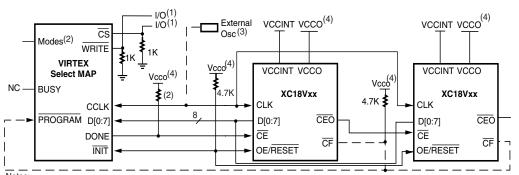

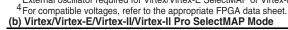

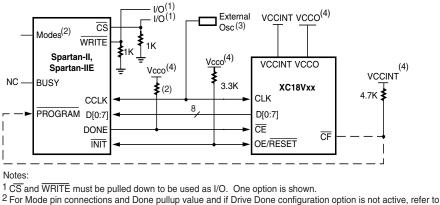

| Master SelectMAP Programming Mode                    | 267 |

| Slave SelectMAP Programming Mode                     | 271 |

| JTAG/ Boundary Scan Programming Mode                 | 275 |

| Configuration Details                                | 293 |

| Readback                                             | 302 |

| Chapter 4: PCB Design Considerations                 |     |

| Summary                                              | 307 |

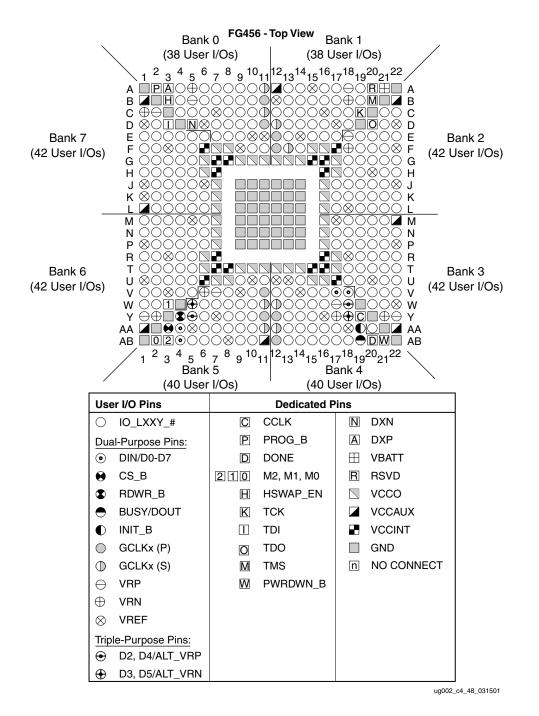

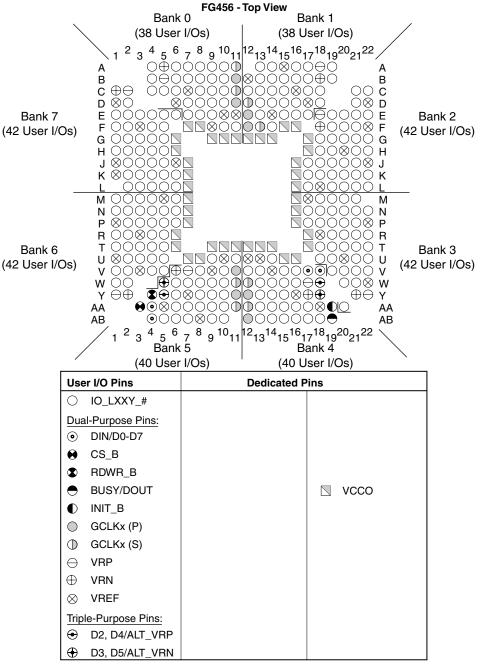

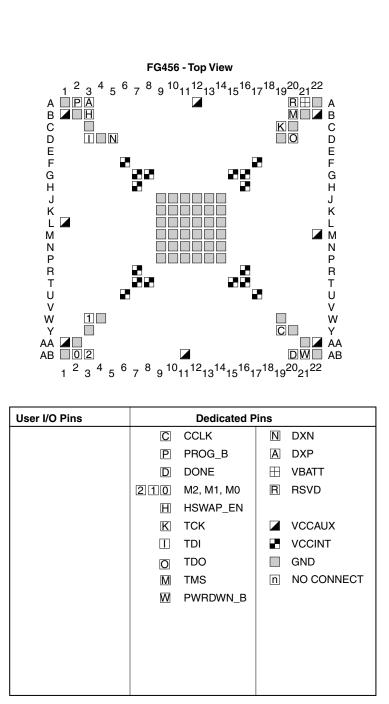

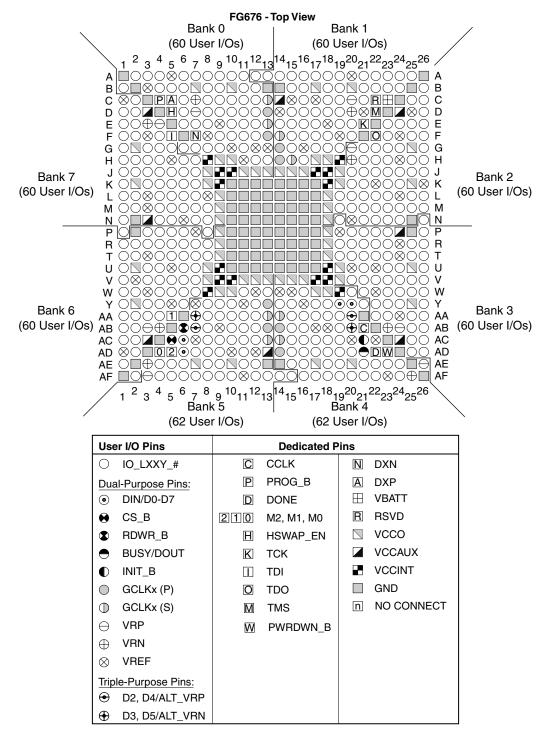

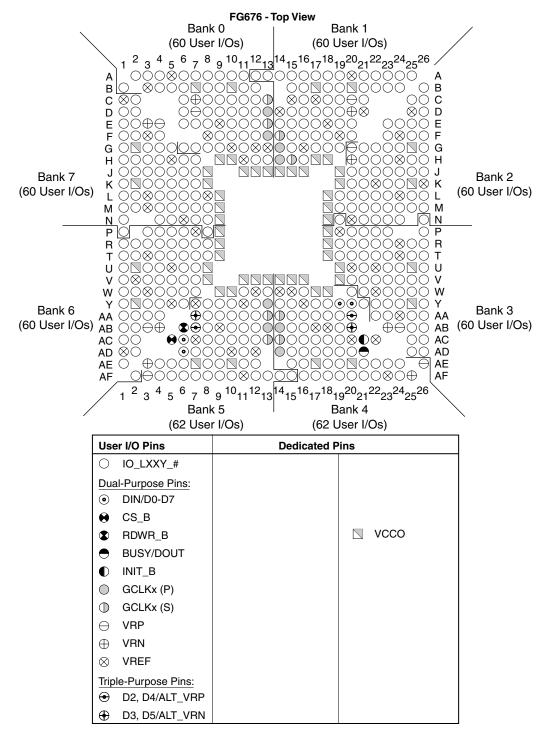

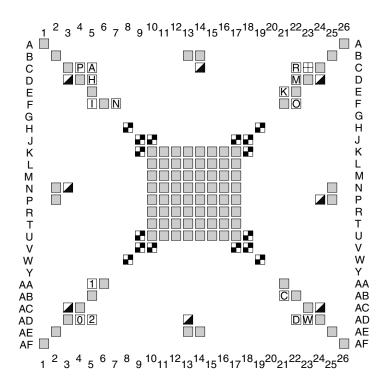

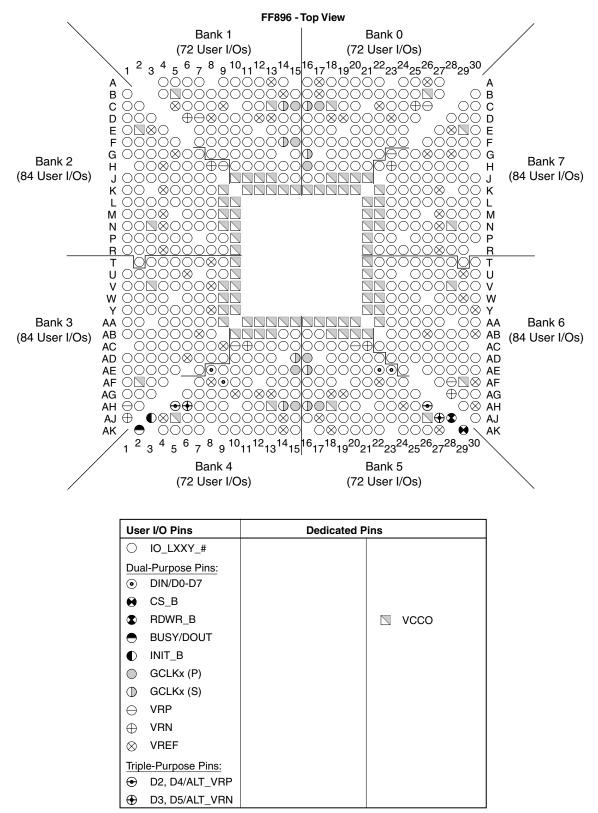

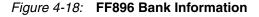

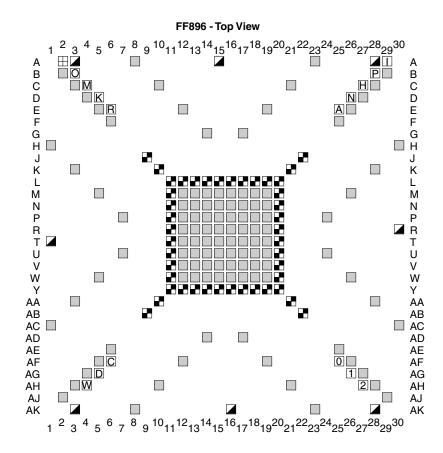

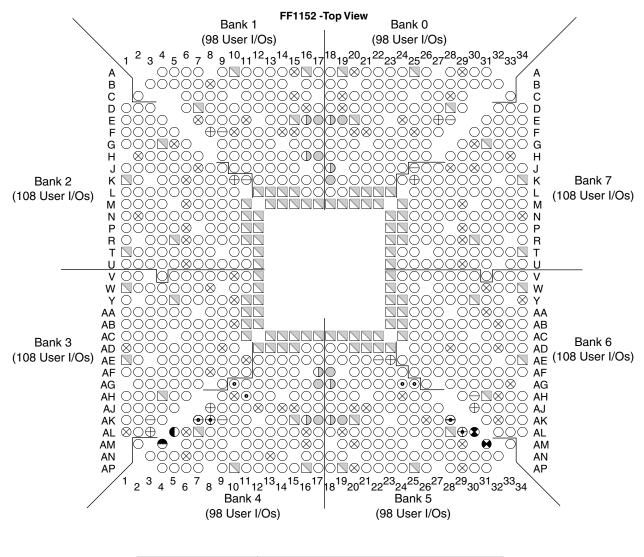

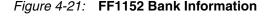

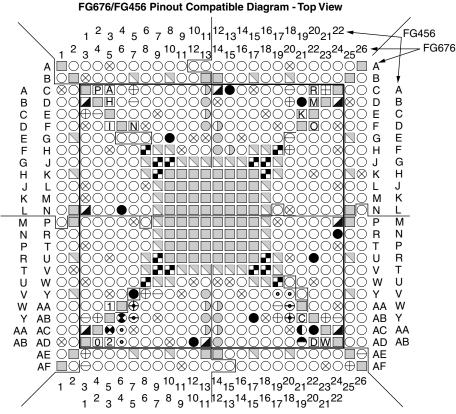

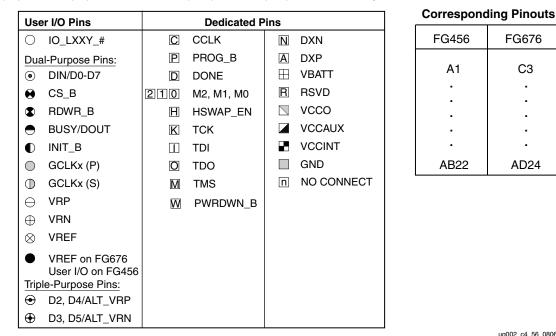

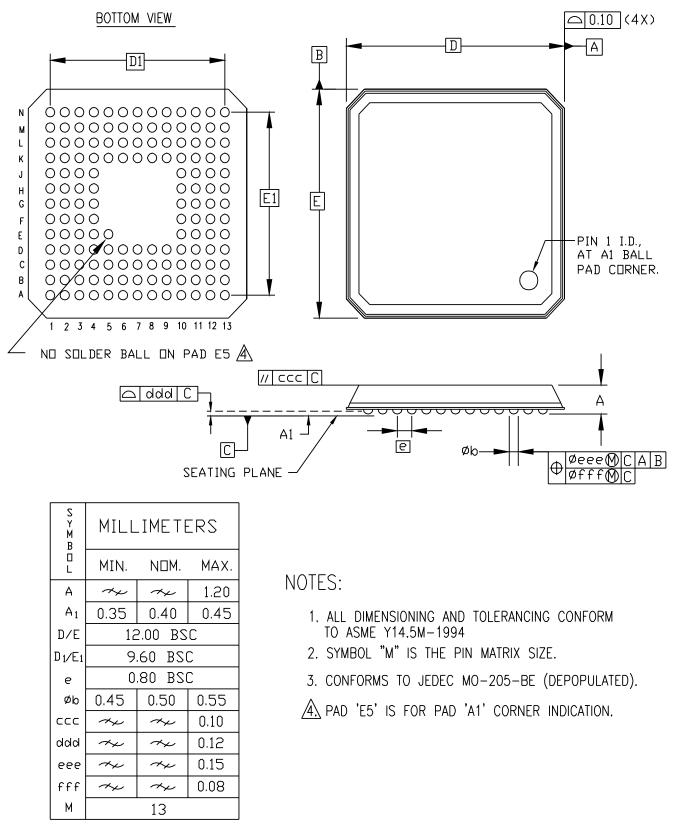

| Pinout Information                                   | 308 |

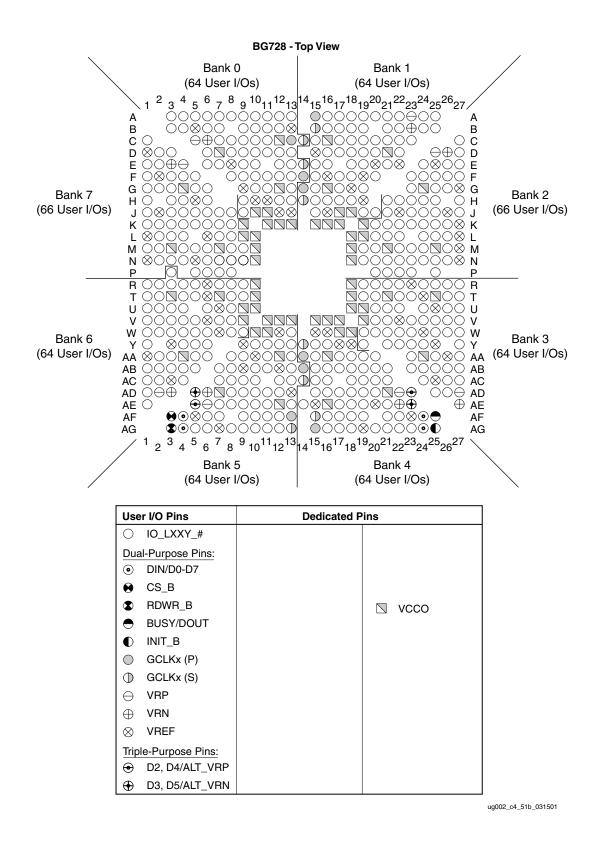

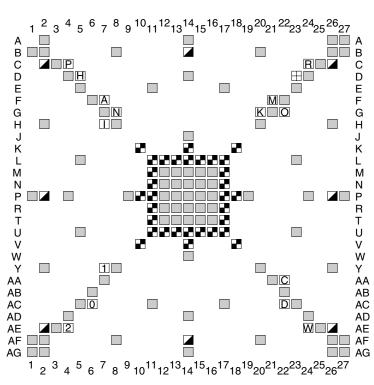

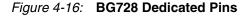

| Pinout Diagrams                                      | 317 |

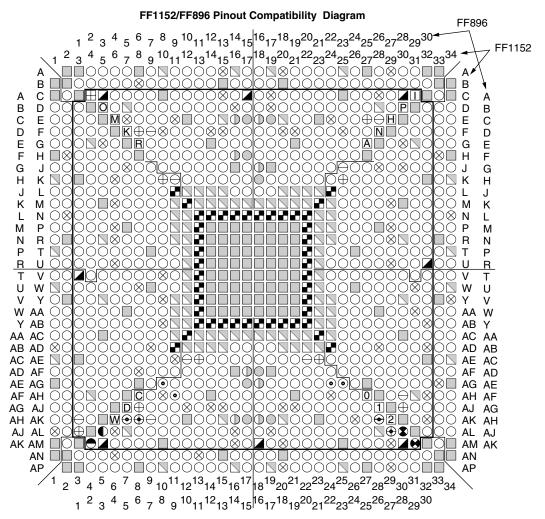

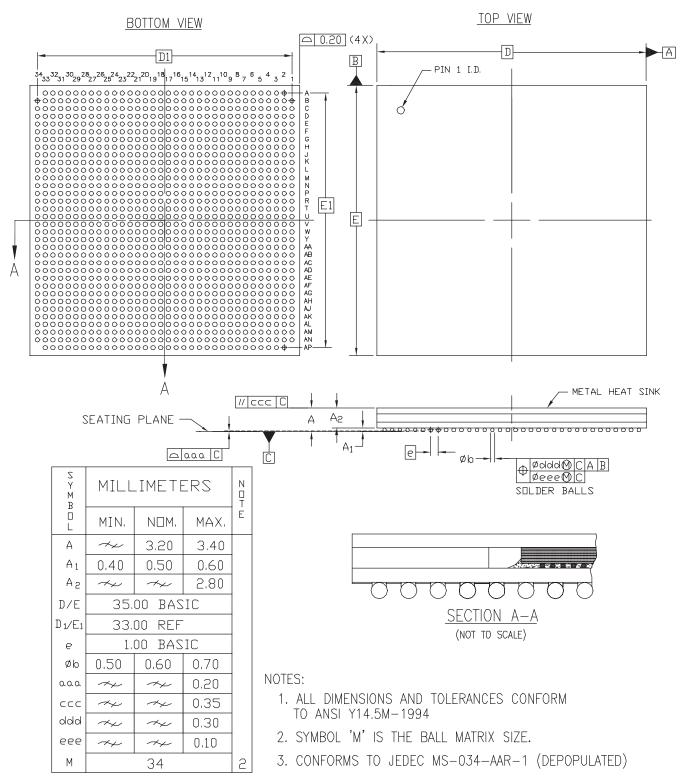

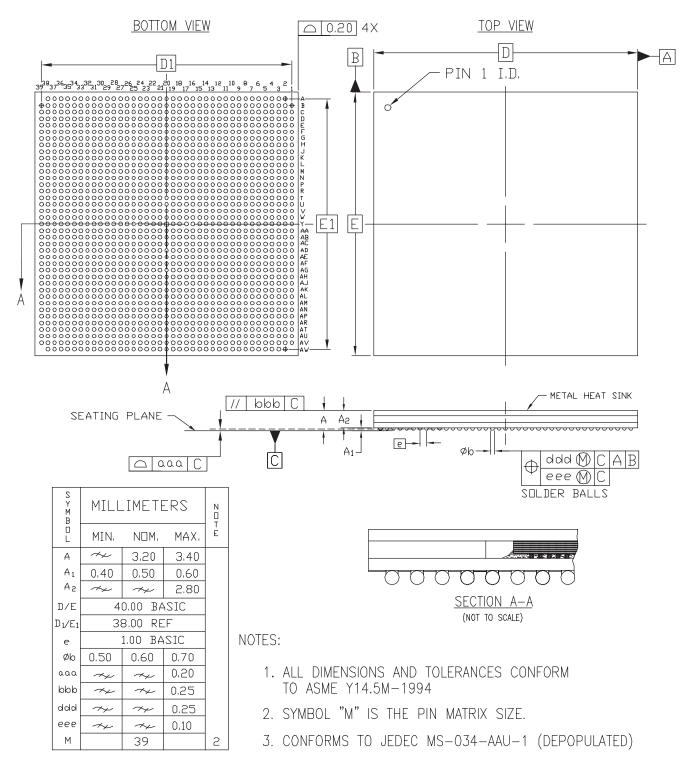

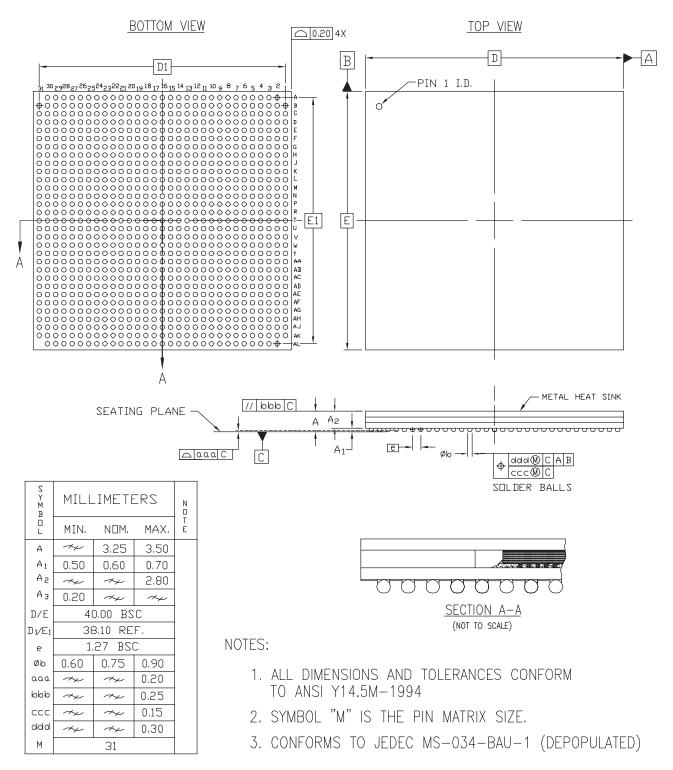

| Package Specifications                               | 357 |

| Flip-Chip Packages                                   | 368 |

| Thermal Data                                         | 369 |

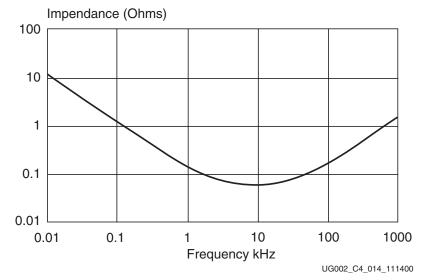

| Printed Circuit Board Considerations                 | 371 |

| Board Routability Guidelines                         | 376 |

| Power Consumption                                    | 398 |

| IBIS Models                                          | 406 |

| BSDL and Boundary Scan Models 4                      | 411 |

| Appendix A: BitGen and PROMGen Switches and Options  |     |

| Using BitGen                                         | 413 |

| Using PROMGen                                        |     |

| Appendix B: XC18V00 Series PROMs                     |     |

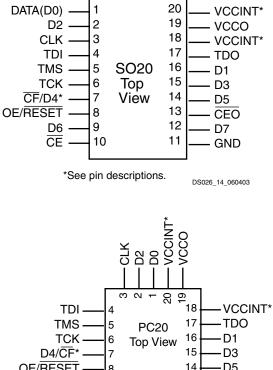

| PROM Package Specifications                          | 427 |

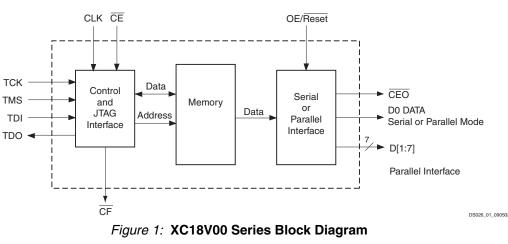

# XC18V00 Series In-System Programmable Configuration PROMs

| Features                          | 431 |

|-----------------------------------|-----|

| Description                       | 431 |

| Pinout and Pin Description        | 432 |

| Pinout Diagrams                   | 434 |

| Xilinx FPGAs and Compatible PROMs | 435 |

| Capacity                          | 436 |

|                                   |     |

# **XILINX**<sup>®</sup>

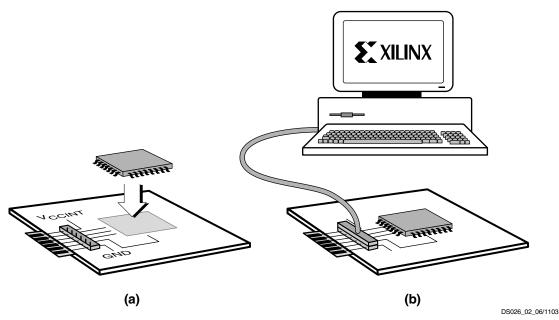

| In-System Programming 43                                                             | \$6 |

|--------------------------------------------------------------------------------------|-----|

| External Programming 43                                                              | 36  |

| Reliability and Endurance 43                                                         | \$6 |

| Design Security 43                                                                   | 36  |

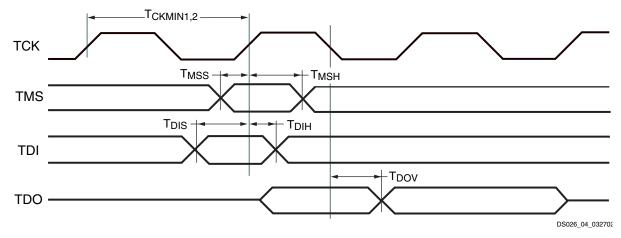

| IEEE 1149.1 Boundary-Scan (JTAG) 43                                                  | 37  |

| Instruction Register 43                                                              | 37  |

| XC18V00 TAP Characteristics 43                                                       | 38  |

| TAP Timing   43                                                                      | 38  |

| TAP AC Parameters    43                                                              | 38  |

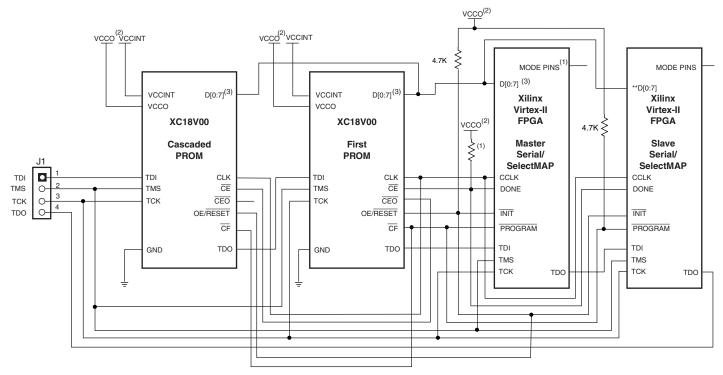

| Connecting Configuration PROMs 43                                                    | ;9  |

| Master Serial Mode Summary 43                                                        | ;9  |

| Reset Activation 44                                                                  | -2  |

| Standby Mode 44                                                                      | -2  |

| 5V Tolerant I/Os 44                                                                  | -2  |

| Customer Control Bits 44                                                             |     |

| Absolute Maximum Ratings <sup>(1,2)</sup>                                            | 3   |

| Recommended Operating Conditions 44                                                  | 3   |

| Quality and Reliability Characteristics                                              | 3   |

| DC Characteristics Over Operating Conditions                                         | 4   |

| AC Characteristics Over Operating Conditions for XC18V04 and XC18V02 44              | 15  |

| AC Characteristics Over Operating Conditions for XC18V01 and XC18V512 44             | 6   |

| AC Characteristics Over Operating Conditions When Cascading for XC18V04 and XC18V02  |     |

| AC Characteristics Over Operating Conditions When Cascading for XC18V01 and XC18V512 |     |

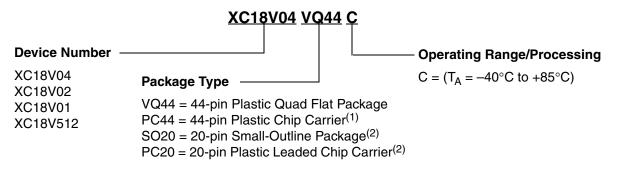

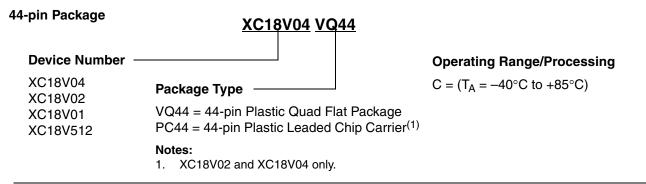

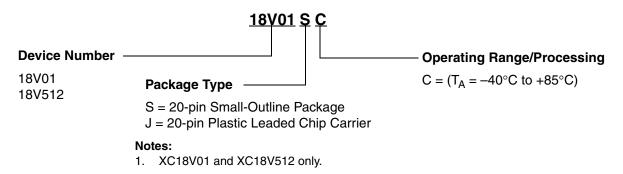

| Ordering Information                                                                 | 9   |

| Valid Ordering Combinations 44                                                       | 9   |

| Marking Information                                                                  | 9   |

| Revision History 45                                                                  | 50  |

| Glossary                                                                             | ;3  |

| Index                                                                                | 53  |

# About This Guide

This document describes the function and operation of Virtex-II devices and also includes information on FPGA configuration techniques and PCB design considerations. For Virtex-II device specifications, refer to the <u>Virtex-II Data Sheet (DS031)</u>.

This guide provides details on the following topics:

- Chapter 1: Timing Models

- Chapter 2: Design Considerations

- Chapter 3: Configuration

- Chapter 4: PCB Design Considerations

- Appendix A: BitGen and PROMGen Switches and Options

- Appendix B: XC18V00 Series PROMs

- Appendix C:

#### **Additional Resources**

The following table lists URLs for resources available on the web. For additional information, go to <u>http://www.xilinx.com</u>.

| Resource             | Description/URL                                                                                                                                                                                                                                                           |  |  |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Handbook             | This site contains the latest <i>Virtex-II User Guide</i> and <i>Virtex-II Data Sheet</i> : <a href="http://www.xilinx.com/products/virtex/handbook/">http://www.xilinx.com/products/virtex/handbook/</a>                                                                 |  |  |

| Application<br>Notes | This site contains device-specific design techniques and approaches:<br>http://www.xilinx.com/apps/appsweb.htm                                                                                                                                                            |  |  |

| Data Book            | <i>The Programmable Logic Data Book</i> describes device-specific information<br>on Xilinx device characteristics, including readback, boundary scan,<br>configuration, length count, and debugging:<br><u>http://www.xilinx.com/xlnx/xweb/xil_publications_index.jsp</u> |  |  |

| Xcell Journals       | This site contains quarterly journals for Xilinx programmable logic users <a href="http://www.xilinx.com/xcell/xcell.htm">http://www.xilinx.com/xcell/xcell.htm</a>                                                                                                       |  |  |

| Tech Tips            | See this site for the latest news, design tips, and patch information on the Xilinx design environment:<br>http://www.xilinx.com/support/techsup/journals/index.htm                                                                                                       |  |  |

| Answers<br>Database  | This database provides a current listing of solution records for Xilinx software tools. Search this database using the search function at: <a href="http://www.xilinx.com/support/searchtd.htm">http://www.xilinx.com/support/searchtd.htm</a>                            |  |  |

# **Typographical Conventions**

The following typographical conventions are used in this manual:

- Red text indicates a cross-reference to information within this document. Click red text to open the specified cross-reference.

- <u>Blue-underlined text</u> indicates a link to a Web page. Click blue-underlined text to browse the specified Web site.

- Courier font indicates prompts or program outputs displayed by the system. speed grade: 5

- **Courier bold** indicates literal commands that you enter in a syntactical statement. However, braces "{}" in Courier bold are not literal and square brackets "[]" in Courier bold are literal only in the case of bus specifications, such as bus [7:0].

```

rpt_del_net=

```

Courier bold also indicates menu commands: File  $\rightarrow$  Open

- *Italic font* denotes the following items:

- Variables that are substituted with user-defined values edif2ngd design\_name

- References to other documents. See the *Libraries Guide* for more information.

- Emphasis in text If a wire is drawn so that it overlaps the pin of a symbol, the two nets are *not* connected.

- Square brackets "[]" indicate an optional entry or parameter. However, in bus specifications, such as bus [7:0], they are required.

edif2ngd [option\_name] design\_name

- Braces "{ }" enclose a list of items from which you must choose one or more, and a vertical bar " | " separates items in a list of choices:

lowpwr ={on | off}

- A vertical ellipsis indicates repetitive material that has been omitted.

```

IOB #1: Name = QOUT'

IOB #2: Name = CLKIN'

.

.

```

• A horizontal ellipsis "..." indicates that an item can be repeated one or more times. allow block *block\_name loc1 loc2 ... locn;*

#

# Introduction to the Virtex-II FPGA Family

# **Virtex-II Platform**

The Virtex-II Platform FPGA solution is the result of the largest silicon and software R&D effort in the history of programmable logic, with the goal of revolutionizing the design of complex single-chip sub-systems in terms of engineering productivity, silicon efficiency, and system flexibility.

The Virtex-II product family provides IP-Immersion<sup>TM</sup> technology which incorporates an abundance of on-chip memory options and advanced routing resources for supporting complex designs that use IP (intellectual property), such as on-chip hard-macro building blocks and a rapidly growing library of soft-IP blocks. For the first time in the programmable logic industry, innovative Virtex-II features enable system designers to:

- Eliminate external termination resistors with on-chip precision-controlled output impedance

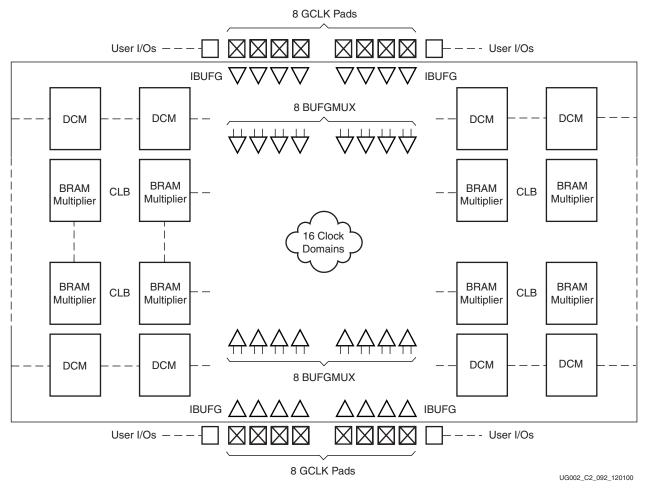

- Manage 16 pre-engineered low-skew clock domains, with on-chip frequency and phase control

- Protect chip designs with bit-stream encryption

These unique capabilities increase engineering productivity and time-to-production by supply pre-engineered solutions for signal integrity and RF noise challenges, as well as providing a secure means to deliver designs rapidly to production.

The Virtex-II Platform FPGA family is a complete programmable solution that allows digital system designers to rapidly implement a single-chip solution with density up to 10 million system gates, in weeks rather than months or years. The inherent flexibility of Xilinx FPGA devices allows unlimited design changes throughout the development and production phases of the system, with important benefits in improved productivity, reduced design risk, and higher system flexibility. This further accelerates the industry -- from custom ASICs to FPGAs -- in fields such as optical networking systems, gigabit routers, wireless cellular base stations, modem arrays, and professional video broadcast systems.

### **Virtex-II Target Applications**

The Virtex-II solution is developed specifically to enable rapid development of two of the most technically challenging digital system applications: data communications and digital signal processing (DSP) systems. High logic integration, fast and complex routing of wide busses, and extensive pipeline and FIFO memory requirements characterize these systems.

The Virtex-II family incorporates high logic capacity, up to 10 million system gates, a new Active Interconnect<sup>TM</sup> architecture optimized for predictable routing delays, an advanced memory array architecture with up to 4.5Mbits of on-chip memory, and built-in support for high-speed I/O standards at up to 1108 user pins.

Applications incorporating DSP functionality, such as echo cancellation, forward errorcorrection, and image compression/decompression, benefit from the abundance of embedded high-speed 18-bit x 18-bit multiplier blocks within the Virtex-II solution. The unique features of the revolutionary Virtex-II architecture make it ideal for optical networking products, storage area networks (SANs), Voice-over-Internet-Protocol (VoIP), video broadcasting, medical imaging, wireless base-stations, and Internet infrastructure products, as well as many other products.

# Interconnect Engine for Fast, Wide Busses in Networking Applications

The Virtex-II architecture incorporates a number of novel features specifically to support wide data widths in complex networking and transmission systems. Modern complex systems operate with multiple clock domains, with large IP-based subsystems operating independently. Large, wide FIFOs and buffer memories are needed for handling fast and wide inter-subsystem data transfer. These wide busses are required both internally for intra-chip communications and externally for switched fabric communications.

For example, wide 32-bit and larger data busses can drive multiple Ultra Low-Voltage Differential Signal (ULVDS) high-speed interface standards for data transfer across a backplane or for point-to-point communications, or be used for implementing high-speed multi-cast bus standards.

These requirements challenge and exceed the capabilities of current programmable logic devices, which lack the gate capacity, memory and routing resources, performance, and architecture flexibility to fully support these designs. The Virtex-II solution is the first platform FPGA specifically targeted to improve the "ease of speed" in the development and production of these complex systems.

### **Complete Solution For Rapid Time-to-Production**

The Virtex-II solution combines the most flexible FPGA architecture, advanced process technology, powerful software synthesis technology, and robust IP library, to provide the most complete system integration solution today. In addition, the Virtex-II solution provides powerful features, such as Xilinx Digitally Controlled Impedance (DCI) technology, digital clock manager to help designers further reduce overall system cost and design development cycle, making Virtex-II the ideal solution for tomorrow's high-performance system designs.

# Chapter 1

# **Timing Models**

# Summary

The following topics are covered in this chapter:

- CLB / Slice Timing Model

- Block SelectRAM Timing Model

- Embedded Multiplier Timing Model

- IOB Timing Model

- Pin-to-Pin Timing Model

- Digital Clock Manager Timing Model

#### Introduction

Due to the large size and complexity of Virtex-II FPGAs, understanding the timing associated with the various paths and functional elements has become a difficult and important problem. Although it is not necessary to understand the various timing parameters in order to implement most designs using Xilinx, Inc. software, a thorough timing model can assist advanced users in analyzing critical paths, or planning speed-sensitive designs.

The Timing Model chapter is broken up into five sections consisting of three basic components:

- Functional Element Diagram basic architectural schematic illustrating pins and connections.

- Timing Parameters <u>Virtex-II Data Sheet (DS031</u>) timing parameter definitions.

- Timing Diagram illustrates functional element timing parameters relative to each other.

This chapter was written with the Xilinx Timing Analyzer software (TRCE) in mind. All pin names, parameter names, and paths are consistent with Post Route Timing and Pre-Route Static Timing reports. Use the models in this chapter in conjunction with both the Timing Analyzer software and the section on switching characteristics in the *Virtex-II Data Sheet*. Most of the timing parameters found in the section on switching characteristics are described in this chapter.

# **CLB / Slice Timing Model**

#### Introduction

This section describes all timing parameters reported in the <u>Virtex-II Data Sheet (DS031</u>) that are associated with slices and Configurable Logic Blocks (CLBs). It consists of three parts corresponding to their respective (switching characteristics) sections in the data sheet:

- General Slice Timing Model and Parameters (CLB Switching Characteristics)

- Slice Distributed RAM Timing Model and Parameters (CLB Distributed RAM Switching Characteristics)

- Slice SRL Timing Model and Parameters (CLB SRL Switching Characteristics)

#### General Slice Timing Model and Parameters

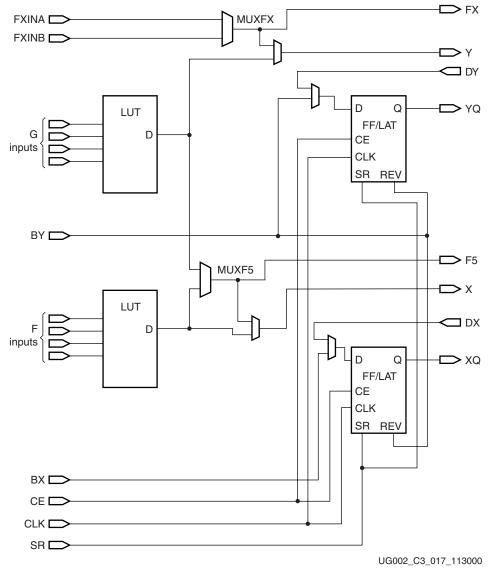

Figure 1-1 illustrates the details of a Virtex-II slice.

Note: Some elements of the Virtex-II slice have been omitted for clarity. Only the elements relevant to the timing paths described in this section are shown.

# **Timing Parameters**

| Parameter                                                                                              | Function                                       | Control<br>Signal | Description                                                                                                                                                                   |  |  |  |

|--------------------------------------------------------------------------------------------------------|------------------------------------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Combinatorial                                                                                          | Combinatorial Delays                           |                   |                                                                                                                                                                               |  |  |  |

| T <sub>ILO</sub>                                                                                       | F/G inputs to X/Y outputs                      |                   | Propagation delay from the F/G inputs of<br>the slice, through the look-up tables<br>(LUTs), to the X/Y outputs of the slice.                                                 |  |  |  |

| T <sub>IF5</sub>                                                                                       | F/G inputs to F5<br>output                     |                   | Propagation delay from the F/G inputs of the slice, through the LUTs and MUXF5 to the F5 output of the slice.                                                                 |  |  |  |

| T <sub>IF5X</sub>                                                                                      | F/G inputs to X<br>output                      |                   | Propagation delay from the F/G inputs of the slice, through the LUTs and MUXF5 to the X output of the slice.                                                                  |  |  |  |

| T <sub>IFXY</sub>                                                                                      | FXINA/FXINB<br>inputs to Y<br>output           |                   | Propagation delay from the<br>FXINA/FXINB inputs, through MUXFX<br>to the Y output of the slice.                                                                              |  |  |  |

| T <sub>IFNCTL</sub>                                                                                    | Transparent<br>Latch input to<br>XQ/YQ outputs |                   | Incremental delay through a transparent latch to XQ/YQ outputs.                                                                                                               |  |  |  |

| Sequential Del                                                                                         | ays                                            |                   |                                                                                                                                                                               |  |  |  |

| T <sub>CKO</sub>                                                                                       | FF Clock (CLK)<br>to XQ/YQ<br>outputs          |                   | Time after the clock that data is stable at the XQ/YQ outputs of the slice sequential elements (configured as a flip-flop).                                                   |  |  |  |

| T <sub>CKLO</sub>                                                                                      | Latch Clock<br>(CLK) to<br>XQ/YQ outputs       |                   | Time after the clock that data is stable at<br>the XQ/YQ outputs of the slice sequential<br>elements (configured as a latch).                                                 |  |  |  |

| Setup and Hole                                                                                         | d for Slice Sequent                            | tial Elements     | s                                                                                                                                                                             |  |  |  |

| T <sub>xxCK</sub> = Setup time (before clock edge)<br>T <sub>CKxx</sub> = Hold time (after clock edge) |                                                |                   | The following descriptions are for setup times only.                                                                                                                          |  |  |  |

| T <sub>DICK</sub> /T <sub>CKDI</sub>                                                                   | BX/BY inputs                                   |                   | Time before Clock (CLK) that data from<br>the BX or BY inputs of the slice must be<br>stable at the D-input of the slice sequential<br>elements (configured as a flip-flop).  |  |  |  |

| T <sub>DYCK</sub> /T <sub>CKDY</sub>                                                                   | DY input                                       |                   | Time before Clock (CLK) that data from<br>the DY input of the slice must be stable at<br>the D-input of the slice sequential<br>elements (configured as a flip-flop).         |  |  |  |

| T <sub>DXCK</sub> /T <sub>CKDX</sub>                                                                   | DX input                                       |                   | Time before Clock (CLK) that data from<br>the DX input of the slice must be stable at<br>the D-input of the slice sequential<br>elements (configured as a flip-flop).         |  |  |  |

| T <sub>CECK</sub> /T <sub>CKCE</sub>                                                                   | CE input                                       |                   | Time before Clock (CLK) that the CE<br>(Clock Enable) input of the slice must be<br>stable at the CE-input of the slice sequen-<br>tial elements (configured as a flip-flop). |  |  |  |

| Parameter                          | Function     | Control<br>Signal | Description                                                                                                                                                                                                             |

|------------------------------------|--------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| T <sub>RCK</sub> /T <sub>CKR</sub> | SR/BY inputs |                   | Time before CLK that the SR (Set/Reset)<br>and the BY (Rev) inputs of the slice must<br>be stable at the SR/Rev-inputs of the slice<br>sequential elements (configured as a flip-<br>flop). Synchronous set/reset only. |

| Clock CLK                          |              |                   |                                                                                                                                                                                                                         |

| T <sub>CH</sub>                    |              |                   | Minimum Pulse Width, High.                                                                                                                                                                                              |

| T <sub>CL</sub>                    |              |                   | Minimum Pulse Width, Low.                                                                                                                                                                                               |

| Set/Reset                          |              |                   |                                                                                                                                                                                                                         |

| T <sub>RPW</sub>                   |              |                   | Minimum Pulse Width for the SR<br>(Set/Reset) and BY (Rev) pins.                                                                                                                                                        |

| T <sub>RQ</sub>                    |              |                   | Propagation delay for an asynchronous<br>Set/Reset of the slice sequential elements.<br>From SR/BY inputs to XQ/YQ outputs.                                                                                             |

| F <sub>TOG</sub>                   |              |                   | Toggle Frequency - Maximum Frequency that a CLB flip-flop can be clocked: $1/(T_{CH}+T_{CL})$                                                                                                                           |

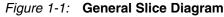

Figure 1-2 illustrates general timing characteristics of a Virtex-II slice.

Figure 1-2: General Slice Timing Diagram

- At time T<sub>CECK</sub> before Clock Event 1, the Clock-Enable signal becomes valid-high at the CE input of the slice register.

- At time T<sub>DYCK</sub> before Clock Event 1, data from the DY input becomes valid-high at the D input of the slice register and is reflected on the YQ pin at time T<sub>CKO</sub> after Clock Event 1\*.

- At time T<sub>RCK</sub> before Clock Event 3, the SR signal (configured as synchronous reset in this case) becomes valid-high, resetting the slice register, and this is reflected on the YQ pin at time T<sub>CKO</sub> after Clock Event 3.

\* NOTE: In most cases software uses the DX/DY inputs to route data to the slice registers when at all possible. This is the fastest path to the slice registers and saves other slice routing resources.

#### Slice Distributed RAM Timing Model and Parameters

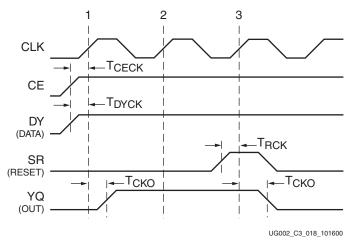

Figure 1-3 illustrates the details of distributed RAM implemented in a Virtex-II slice.

Note: Some elements of the Virtex-II slice have been omitted for clarity. Only the elements relevant to the timing paths described in this section are shown.

Figure 1-3: Slice Distributed RAM Diagram

# **Timing Parameters**

| Parameter                          | Function                                               | Control<br>Signal | Description                                                                                                                                            |  |

|------------------------------------|--------------------------------------------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Sequential I                       | Delays for Slice LUT C                                 | onfigured a       | s RAM (Distributed RAM)                                                                                                                                |  |

| T <sub>SHCKO16</sub>               | CLK to X/Y outputs<br>(WE active) in 16x1<br>mode      |                   | Time after the Clock (CLK) of a WRITE operation that the data written to the distributed RAM (in 16x1 mode) is stable on the X/Y outputs of the slice. |  |

| T <sub>SHCKO32</sub>               | CLK to X/Y outputs<br>(WE active) in 32x1<br>mode      |                   | Time after the Clock (CLK) of a WRITE operation that the data written to the distributed RAM (in 32x1 mode) is stable on the X/Y outputs of the slice. |  |

| T <sub>SHCKOF5</sub>               | CLK to F5 output<br>(WE active)                        |                   | Time after the Clock (CLK) of a WRITE operation that the data written to the distributed RAM is stable on the F5 output of the slice.                  |  |

| Setup and H                        | old for Slice LUT Con                                  | figured as R      | AM (Distributed RAM)                                                                                                                                   |  |

|                                    | ıp time (before clock edg<br>ld time (after clock edge |                   | The following descriptions are for setup times only.                                                                                                   |  |

| T <sub>DS</sub> /T <sub>DH</sub>   | BX/BY Data inputs<br>(DI)                              |                   | Time before the clock that data must be<br>stable at the DI input of the slice LUT<br>(configured as RAM), via the slice<br>BX/BY inputs.              |  |

| $T_{AS}/T_{AH}$                    | F/G Address inputs                                     |                   | Time before the clock that address signals must be stable at the F/G inputs of the slice LUT (configured as RAM).                                      |  |

| T <sub>WES</sub> /T <sub>WEH</sub> | WE input (SR)                                          |                   | Time before the clock that the Write<br>Enable signal must be stable at the WE<br>input of the slice LUT (configured as<br>RAM).                       |  |

| Clock CLK                          |                                                        |                   |                                                                                                                                                        |  |

| T <sub>WPH</sub>                   |                                                        |                   | Minimum Pulse Width, High (for a Distributed RAM clock).                                                                                               |  |

| T <sub>WPL</sub>                   |                                                        |                   | Minimum Pulse Width, Low (for a Distributed RAM clock).                                                                                                |  |

| T <sub>WC</sub>                    |                                                        |                   | Minimum clock period to meet address write cycle time.                                                                                                 |  |

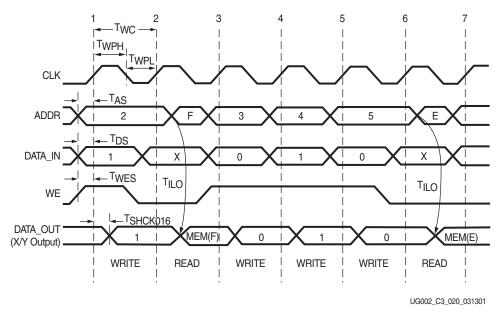

Figure 1-4 illustrates the timing characteristics of a 16-bit distributed RAM implemented in a Virtex-II slice (LUT configured as RAM).

Figure 1-4: Slice Distributed RAM Timing Diagram

#### Clock Event 1: WRITE Operation

During a WRITE operation, the contents of the memory at the address on the ADDR inputs is changed. The data written to this memory location is reflected on the X/Y outputs synchronously.

- At time T<sub>WES</sub> before Clock Event 1, the Write Enable signal (WE) becomes valid-high, enabling the RAM for the following WRITE operation.

- At time T<sub>AS</sub> before Clock Event 1, the address (2) becomes valid at the F/G inputs of the RAM.

- At time T<sub>DS</sub> before Clock Event 1, the DATA becomes valid (1) at the DI input of the RAM and is reflected on the X/Y output at time T<sub>SHCKO16</sub> after Clock Event 1.

#### **Clock Event 2: READ Operation**

All READ operations are asynchronous in distributed RAM. As long as write-enable (WE) is Low, the address bus can be asserted at any time, and the contents of the RAM at that address are reflected on the X/Y outputs after a delay of length  $T_{ILO}$  (propagation delay through a LUT). Note that the Address (F) is asserted *after* Clock Event 2, and that the contents of the RAM at that location are reflected on the output after a delay of length  $T_{ILO}$ .

# Slice SRL Timing Model and Parameters

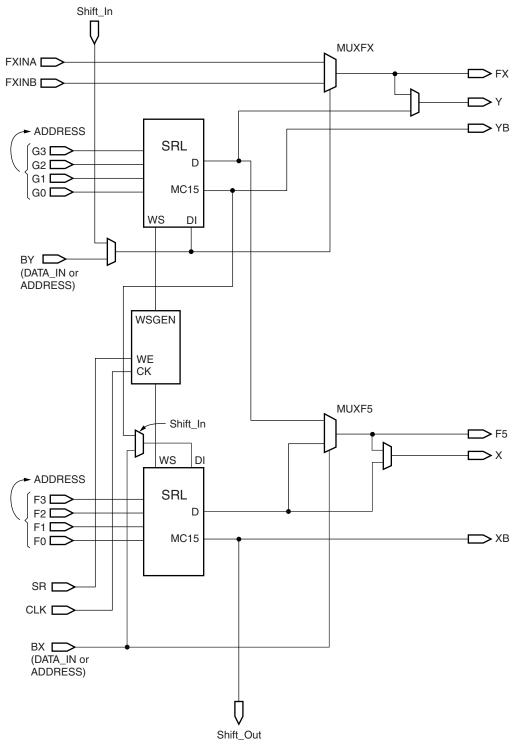

Figure 1-5 illustrates shift register implementation in a Virtex-II slice.

Note: Some elements of the Virtex-II slice have been omitted for clarity. Only the elements relevant to the timing paths described in this section are shown.

UG002\_C3\_021\_113000

Figure 1-5: Slice SLR Diagram

www.xilinx.com

1-800-255-7778

#### **Timing Parameters**

| Parameter                                                                              | Function                                                                  | Control<br>Signal | Description                                                                                                                               |  |  |

|----------------------------------------------------------------------------------------|---------------------------------------------------------------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Sequential I                                                                           | Sequential Delays for Slice LUT Configured as SRL (Select Shift Register) |                   |                                                                                                                                           |  |  |

| T <sub>REG</sub>                                                                       | CLK to<br>X/Y outputs                                                     |                   | Time after the Clock (CLK) of a WRITE operation that the data written to the SRL is stable on the X/Y outputs of the slice.               |  |  |

| T <sub>CKSH</sub>                                                                      | CLK to Shiftout                                                           |                   | Time after the Clock (CLK) of a WRITE operation that the data written to the SRL is stable on the Shiftout or XB/YB outputs of the slice. |  |  |

| T <sub>REGF5</sub>                                                                     | CLK to F5 output                                                          |                   | Time after the Clock (CLK) of a WRITE operation that the data written to the SRL is stable on the F5 output of the slice.                 |  |  |

| Setup/Hold                                                                             | for Slice LUT Confi                                                       | gured as S        | RL (Select Shift Register)                                                                                                                |  |  |

| $T_{xxS}$ = Setup time (before clock edge)<br>$T_{xxH}$ = Hold time (after clock edge) |                                                                           |                   | The following descriptions are for setup times only.                                                                                      |  |  |

| T <sub>SRLDS</sub> /<br>T <sub>SRLDH</sub>                                             | BX/BY Data<br>inputs (DI)                                                 |                   | Time before the clock that data must be stable<br>at the DI input of the slice LUT (configured as<br>SRL), via the slice BX/BY inputs.    |  |  |

| T <sub>WSS</sub> /T <sub>WSH</sub>                                                     | CE input (WE)                                                             |                   | Time before the clock that the Write Enable<br>signal must be stable at the WE input of the<br>slice LUT (configured as SRL).             |  |  |

| Clock CLK                                                                              |                                                                           |                   |                                                                                                                                           |  |  |

| T <sub>SRPH</sub>                                                                      |                                                                           |                   | Minimum Pulse Width, High (for an SRL clock).                                                                                             |  |  |

| T <sub>SRPL</sub>                                                                      |                                                                           |                   | Minimum Pulse Width, Low (for an SRL clock).                                                                                              |  |  |

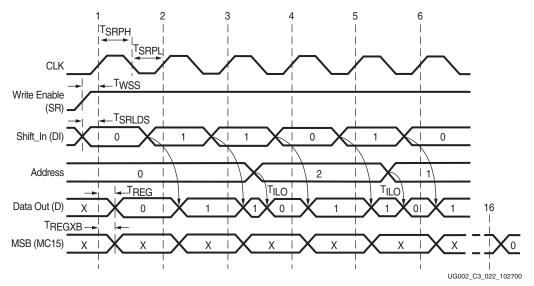

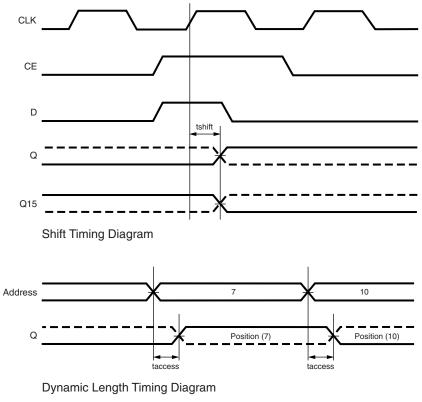

Figure 1-6 illustrates the timing characteristics of a 16-bit shift register implemented in a Virtex-II slice (LUT configured as SRL).

#### Clock Event 1: Shift\_In

During a WRITE (Shift\_In) operation, the single-bit content of the register at the address on the ADDR inputs is changed, as data is shifted through the SRL. The data written to this register is reflected on the X/Y outputs synchronously, if the address is unchanged during the clock event. If the ADDR inputs are changed during a clock event, the value of the data at the addressable output (D) is invalid.

- At time T<sub>WSS</sub> before Clock Event 1, the Write Enable signal (SR) becomes valid-high, enabling the SRL for the WRITE operation that follows.

- At time T<sub>SRLDS</sub> before Clock Event 1 the data becomes valid (0) at the DI input of the SRL and is reflected on the X/Y output after a delay of length T<sub>REG</sub> after Clock Event 1\*.

\* Note: Since the address 0 is specified at Clock Event 1, the data on the DI input is reflected at the D output, because it is written to Register 0.

#### Clock Event 2: Shift\_In

At time T<sub>SRLDS</sub> before Clock Event 2, the data becomes valid (1) at the DI input of the SRL and is reflected on the X/Y output after a delay of length T<sub>REG</sub> after Clock Event 2\*.

\* Note: Since the address 0 is still specified at Clock Event 2, the data on the DI input is reflected at the D output, because it is written to Register 0.

#### Clock Event 3: Shift\_In / Addressable (Asynchronous) READ

All READ operations are asynchronous. If the address is changed (between clock events), the contents of the register at that address are reflected at the addressable output (X/Y outputs) after a delay of length  $T_{ILO}$  (propagation delay through a LUT).

- At time T<sub>SRLDS</sub> before Clock Event 3 the Data becomes valid (1) at the DI input of the SRL, and is reflected on the X/Y output T<sub>REG</sub> time after Clock Event 3.

- Notice that the address is changed (from 0 to 2) some time after Clock Event 3. The value stored in Register 2 at this time is a 0 (in this example, this was the first data shifted in), and it is reflected on the X/Y output after a delay of length T<sub>ILO</sub>.

#### Clock Event 16: MSB (Most Significant Bit) Changes

• At time T<sub>REGXB</sub> after Clock Event 16, the first bit shifted into the SRL becomes valid (logical 0 in this case) on the XB output of the slice via the MC15 output of the LUT (SRL).

# **Block SelectRAM Timing Model**

#### Introduction

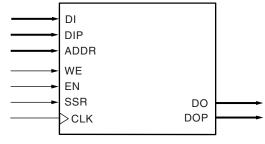

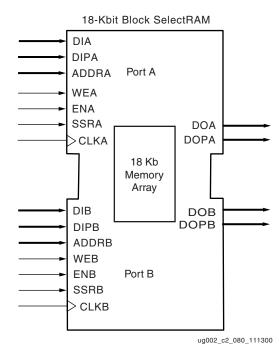

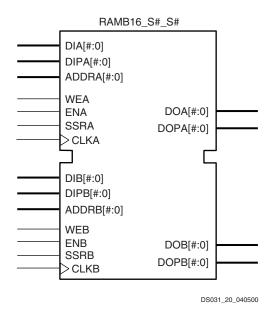

This section describes the timing parameters associated with the block SelectRAM (illustrated in Figure 1-7) in Virtex-II FPGA devices. This section is intended to be used with the section on switching characteristics in the <u>Virtex-II Data Sheet (DS031)</u> and the Timing Analyzer (TRCE) report from Xilinx software. For specific timing parameter values, refer to the switching characteristics section in the *Virtex-II Data Sheet*.

DS031\_10\_071602

Figure 1-7: Block SelectRAM Block Diagram

#### **Timing Parameters**

| Parameter                                                                                | Function Control Signal  |              | Description                                                                                                   |  |  |

|------------------------------------------------------------------------------------------|--------------------------|--------------|---------------------------------------------------------------------------------------------------------------|--|--|

| Setup and Hold F                                                                         | Relative to Clock        | (CLK)        |                                                                                                               |  |  |

| $T_{BxCK}$ = Setup time (before clock edge)<br>$T_{BCKx}$ = Hold time (after clock edge) |                          |              | The following descriptions are for setup times only.                                                          |  |  |

| T <sub>BACK</sub> /T <sub>BCKA</sub>                                                     | Address inputs           | ADDR         | Time before the clock that address signals<br>must be stable at the ADDR inputs of the<br>block RAM.          |  |  |

| T <sub>BDCK</sub> /T <sub>BCKD</sub>                                                     | Data inputs              | DI           | Time before the clock that data must be stable at the DI inputs of the block RAM.                             |  |  |

| T <sub>BECK</sub> /T <sub>BCKE</sub>                                                     | Enable                   | EN           | Time before the clock that the enable signal must be stable at the EN input of the block RAM.                 |  |  |

| T <sub>BRCK</sub> /T <sub>BCKR</sub>                                                     | Synchronous<br>Set/Reset | SSR          | Time before the clock that the synchronous set/reset signal must be stable at the SSR input of the block RAM. |  |  |

| T <sub>BWCK</sub> /T <sub>BCKW</sub>                                                     | Write Enable             | WE           | Time before the clock that the write enable signal must be stable at the WE input of the block RAM.           |  |  |

| Clock to Out                                                                             | Clock to Out             |              |                                                                                                               |  |  |

| T <sub>BCKO</sub>                                                                        | Clock to<br>Output       | CLK to<br>DO | Time after the clock that the output data is stable at the DO outputs of the block RAM.                       |  |  |

| Clock                                                                                    | Clock                    |              |                                                                                                               |  |  |

| T <sub>BPWH</sub>                                                                        | Clock                    | CLK          | Minimum pulse width, high.                                                                                    |  |  |

| T <sub>BPWL</sub>                                                                        | Clock                    | CLK          | Minimum pulse width, low.                                                                                     |  |  |

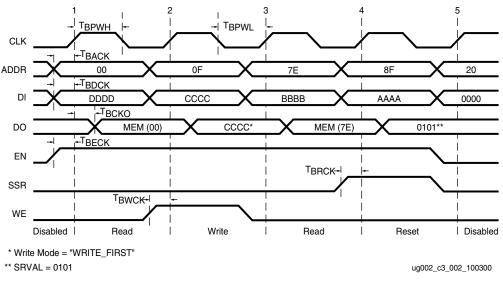

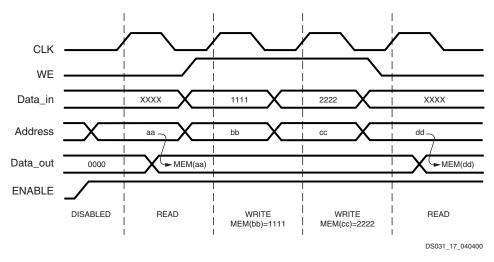

The timing diagram in Figure 1-8 describes a single-port block RAM in Write-First mode. The timing for Read-First and No-Change modes are similar (see chapter 2, block RAM section.)

Figure 1-8: Block SelectRAM Timing Diagram

At time 0, the block RAM is disabled; EN (enable) is low.

#### Clock Event 1

#### **READ Operation:**

During a read operation, the contents of the memory at the address on the ADDR inputs are unchanged.

- T<sub>BACK</sub> before Clock Event 1, address 00 becomes valid at the ADDR inputs of the block RAM.

- At time T<sub>BECK</sub> before Clock Event 1, Enable goes High at the EN input of the block RAM, enabling the memory for the READ operation that follows.

- At time T<sub>BCKO</sub> after Clock Event 1, the contents of the memory at address 00 become stable at the DO pins of the block RAM.

#### Clock Event 2

#### WRITE Operation:

During a write operation, the content of the memory at the location specified by the address on the ADDR inputs is replaced by the value on the DI pins and is immediately reflected on the output latches (in WRITE-FIRST mode); EN (enable) is high.

- At time T<sub>BACK</sub> before Clock Event 2, address 0F becomes valid at the ADDR inputs of the block RAM.

- At time T<sub>BDCK</sub> before Clock Event 2, data CCCC becomes valid at the DI inputs of the block RAM.

- At time T<sub>BWCK</sub> before Clock Event 2, Write Enable becomes valid at the WE following the block RAM.

- At time T<sub>BCKO</sub> after Clock Event 2, data CCCC becomes valid at the DO outputs of the block RAM.

#### Clock Event 4

#### SSR (Synchronous Set/Reset) Operation

During an SSR operation, initialization parameter value SRVAL is loaded into the output latches of the block SelectRAM. The SSR operation does NOT change the contents of the memory and is independent of the ADDR and DI inputs.

- At time T<sub>BRCK</sub> before Clock Event 4, the synchronous set/reset signal becomes valid (High) at the SSR input of the block RAM.

- At time T<sub>BCKO</sub> after Clock Event 4, the SRVAL 0101 becomes valid at the DO outputs of the block RAM.

#### **Clock Event 5**

#### **Disable Operation:**

De-asserting the enable signal EN disables any write, read or SSR operation. The disable operation does NOT change the contents of the memory or the values of the output latches.

- At time T<sub>BECK</sub> before Clock Event 5, the enable signal becomes valid (Low) at the EN input of the block RAM.

- After Clock Event 5, the data on the DO outputs of the block RAM is unchanged.

#### **Timing Model**

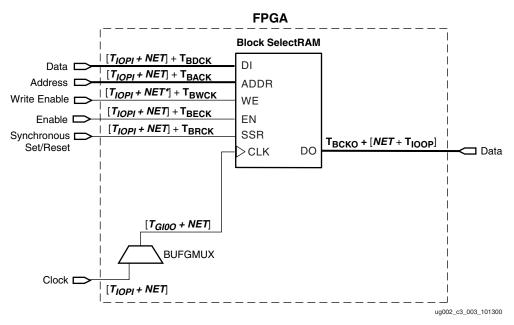

Figure 1-9 illustrates the delay paths associated with the implementation of block SelectRAM. This example takes the simplest paths on and off chip (these paths can vary greatly depending on the design). This timing model demonstrates how and where the block SelectRAM timing parameters are used.

Figure 1-9: Block SelectRAM Timing Model

NET = Varying interconnect delays

T<sub>IOPI</sub> = Pad to I-output of IOB delay

T<sub>IOOP</sub> = O-input of IOB to pad delay

T<sub>GI0O</sub> = BUFGMUX delay

# **Embedded Multiplier Timing Model**

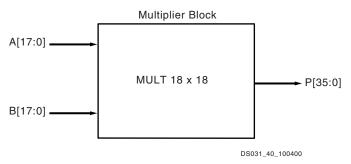

#### Introduction

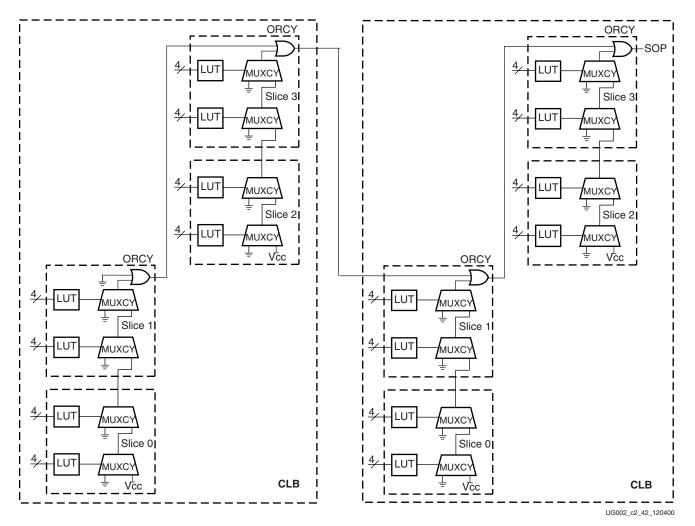

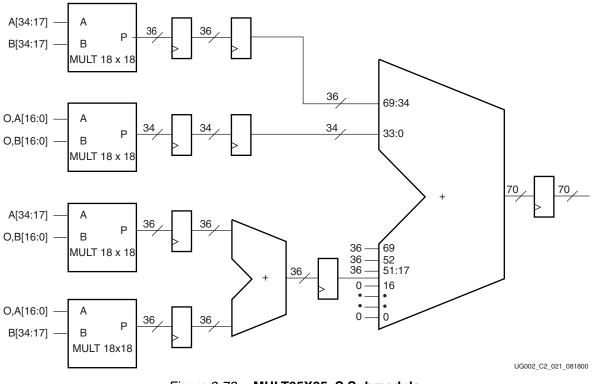

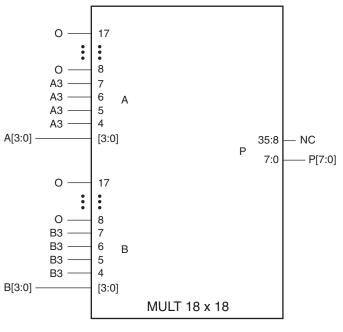

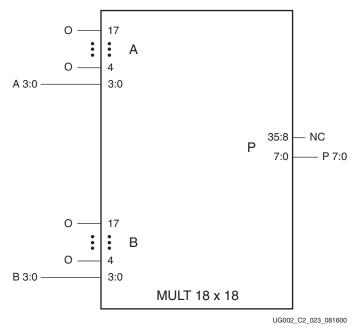

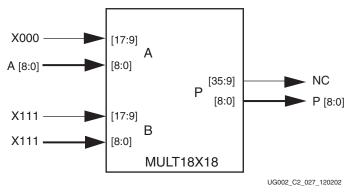

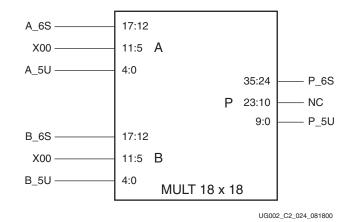

This section explains all timing parameters associated with the use of embedded 18-bit x 18-bit multipliers in Virtex-II FPGAs (see Figure 1-10). The propagation delays through the embedded multiplier differ based on the size of the multiplier function implemented. The longest delay through the multiplier is to the highest order bit output (P35). Therefore, if an 18-bit x 18-bit signed multiplier is implemented, the worst-case delay for this function is the longest delay associated with the embedded multiplier block. If smaller (LSB) multipliers are used, shorter delays can be realized.

This section is intended to be used in conjunction with the section on switching characteristics in the <u>Virtex-II Data Sheet (DS031)</u> and the Timing Analyzer (TRCE) report from Xilinx software. For specific timing parameter values, refer to the *Virtex-II Data Sheet*.

Figure 1-10: Embedded 18-bit x 18-bit Multiplier Block

#### **Timing Parameters**

#### Worst-Case Propagation Delays

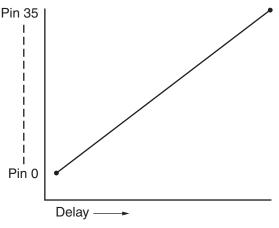

The T<sub>MULT</sub> timing parameter is reported by the Timing Analyzer software. These values correspond to the propagation delay through the multiplier to a specific output pin of the multiplier block. The shortest delay is to pin 0, the longest to pin 35. These parameters can be found in the table entitled "Multiplier Switching Characteristics" in Module 3 of the <u>Virtex-II Platform FPGA Data Sheet</u>. The delay-to-pin ratio is essentially linear (see Figure 1-11). This implies that smaller multiply functions are faster than larger ones. This is true as long as the LSB inputs are used.

UG002\_C3\_023\_092500

Figure 1-11: Pin-to-Delay Ratio Curve

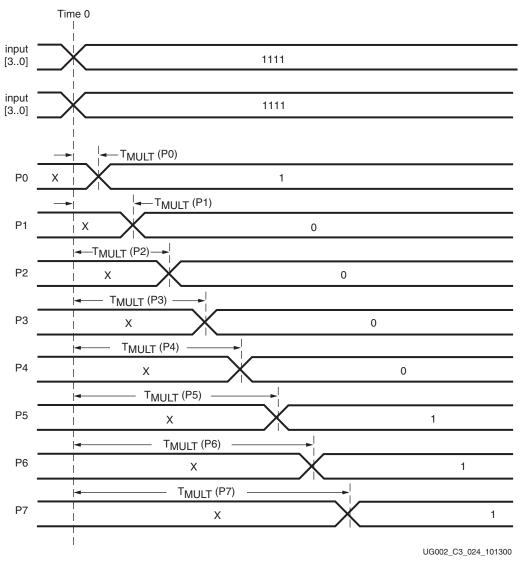

Figure 1-12 illustrates the result (outputs) of a 4-bit x 4-bit unsigned multiply implemented in an embedded multiplier block.

Figure 1-12: Embedded Multiplier Block Timing Diagram

At time 0 the two 4-bit numbers to be multiplied become valid at the A[0..3], B[0..3] inputs to the embedded multiplier. The result appears on the output pins P[0..7] in a staggered fashion. First, P0 becomes valid at time  $T_{MULT}$ (P0), followed by each subsequent output pin, until P7 becomes valid at time  $T_{MULT}$  (P7). In this case, the delay for this multiply function should correspond to that of Pin 7. In other words, the result is not valid until all output pins become valid.

# **IOB Timing Model**

#### Introduction

This section describes all timing parameters associated with the Virtex-II IOB. The section consists of three parts:

- IOB Input Timing Model and Parameters

- IOB Output Timing Model and Parameters

- IOB 3-State Timing Model and Parameters

This section is intended to be used in conjunction with the section on switching characteristics in the <u>Virtex-II Data Sheet (DS031)</u> and the Timing Analyzer (TRCE) report from Xilinx software. For specific timing parameter values, refer to the *Virtex-II Data Sheet*.

#### A Note on I/O Standard Adjustments:

The "IOB Input and Output Switching Characteristics Standard Adjustments" tables in the switching characteristics section of the *Virtex-II Data Sheet* are delay adders (+/-) to be added to all timing parameter values associated with the IOB and the Global Clock (see "Pin-to-Pin Timing Model" on page 38), if an I/O standard other than LVTTL is used.

All values specified in the *Virtex-II Data Sheet* for the parameters covered in this section are specified for LVTTL. If another I/O standard is used, these delays change. However, there are several exceptions. The following parameters associated with the pad going to high-impedance (3-State buffer OFF) should NOT be adjusted:

- T<sub>IOTHZ</sub>

- T<sub>IOTLPHZ</sub>

- T<sub>GTS</sub>

- T<sub>IOCKHZ</sub>

- T<sub>IOSRHZ</sub>

# **IOB** Input Timing Model and Parameters

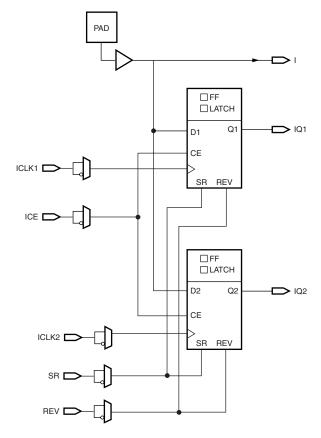

Figure 1-13 illustrates IOB inputs.

UG002\_C3\_004\_101300

Figure 1-13: Virtex-II IOB Input Diagram

#### **Timing Parameters**

| Parameter                                                                                  | Function                  | Control<br>Signal | Description                                                                                                                       |  |  |  |

|--------------------------------------------------------------------------------------------|---------------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Propagation Delays                                                                         | Propagation Delays        |                   |                                                                                                                                   |  |  |  |

| T <sub>IOPI</sub>                                                                          |                           |                   | Propagation delay from the pad to I output of the IOB with no delay adder.                                                        |  |  |  |

| T <sub>IOPID</sub>                                                                         |                           |                   | Propagation delay from the pad to I output of the IOB with the delay adder.                                                       |  |  |  |

| T <sub>IOPLI</sub>                                                                         |                           |                   | Propagation delay from the pad to IQ output of the IOB via transparent latch with no delay adder.                                 |  |  |  |

| T <sub>IOPLID</sub>                                                                        |                           |                   | Propagation delay from the pad to IQ output of the IOB via transparent latch with the delay adder.                                |  |  |  |

| Setup and Hold With Respect to Clock at IOB Input Register                                 |                           |                   |                                                                                                                                   |  |  |  |

| $T_{xxCK}$ = Setup time (before clock edge)<br>$T_{xxCKxx}$ = Hold time (after clock edge) |                           |                   | The following descriptions are for setup times only.                                                                              |  |  |  |

| T <sub>IOPICK</sub> /T <sub>IOICKP</sub>                                                   | ID input with<br>NO delay |                   | Time before the clock that the input signal from the pad must be stable at the ID input of the IOB Input Register, with no delay. |  |  |  |

#

| Parameter                                  | Function                         | Control<br>Signal | Description                                                                                                                       |

|--------------------------------------------|----------------------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| T <sub>IOPICKD</sub> /T <sub>IOICKPD</sub> | ID input with delay              |                   | Time before the clock that the input signal from the pad must<br>be stable at the ID input of the IOB Input Register, with delay. |

| T <sub>IOICECK</sub> /T <sub>IOCKICE</sub> | ICE input                        |                   | Time before the clock that the Clock Enable signal must be stable at the ICE input of the IOB Input Register.                     |

| T <sub>IOSRCKI</sub>                       | SR input (IFF,<br>synchronous)   |                   | Time before the clock that the Set/Reset signal must be stable<br>at the SR input of the IOB Input Register.                      |

| Clock to Out                               |                                  |                   |                                                                                                                                   |

| T <sub>IOCKIQ</sub>                        | Clock (CLK) to<br>(IQ) output    |                   | Time after the clock that the output data is stable at the IQ output of the IOB Input Register.                                   |

| Set/Reset Delays                           |                                  |                   |                                                                                                                                   |

| T <sub>IOSRIQ</sub>                        | SR Input to IQ<br>(asynchronous) |                   | Time after the Set/Reset signal of the IOB is toggled that the output of the IOB input register (IQ) reflects the signal.         |

| T <sub>GSRQ</sub>                          | GSR to output IQ                 |                   | Time after the Global Set/Reset is toggled that the output of the IOB input register (IQ) reflects the set or reset.              |

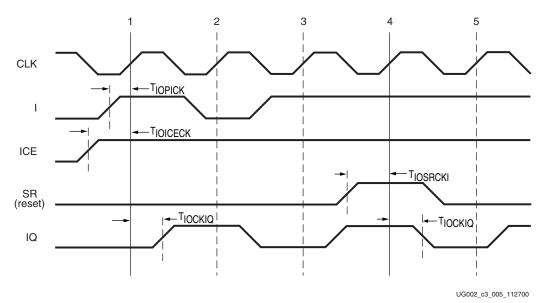

#### Figure 1-14 illustrates IOB input register timing.

Figure 1-14: IOB Input Register Timing Diagram

#### **Clock Events**

- At time T<sub>IOICECK</sub> before Clock Event 1, the input clock enable signal becomes valid-high at the ICE input of the input register, enabling the input register for incoming data.

- At time T<sub>IOPICK</sub> before Clock Event 1, the input signal becomes valid-high at the I input of the input register and is reflected on the IQ output of the input register at time T<sub>IOCKIQ</sub> after Clock Event 1.

- At time T<sub>IOSRCKI</sub> before Clock Event 4 the SR signal (configured as synchronous reset in this case) becomes valid-high resetting the input register and reflected at the IQ output of the IOB at time T<sub>IOCKIQ</sub> after Clock Event 4.

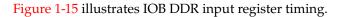

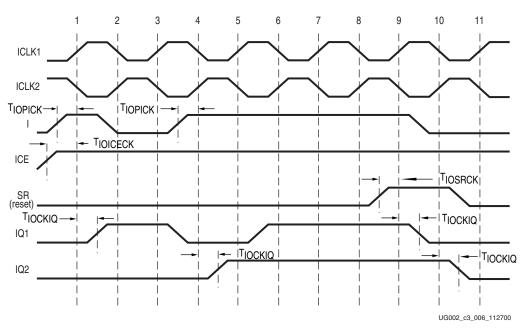

Figure 1-15: IOB DDR Input Register Timing Diagram

#### **Clock Events**

- At time T<sub>IOICECK</sub> before Clock Event 1 the input clock enable signal becomes validhigh at the ICE input of both of the DDR input registers, enabling them for incoming data. Since the ICE and I signals are common to both DDR registers, care must be taken to toggle these signals between the rising edges of ICLK1 and ICLK2 as well as meeting the register setup-time relative to both clocks.

- At time T<sub>IOPICK</sub> before Clock Event 1 (rising edge of ICLK1) the input signal becomes valid-high at the I input of both registers and is reflected on the IQ1 output of input-register 1 at time T<sub>IOCKIQ</sub> after Clock Event 1.

- At time T<sub>IOPICK</sub> before Clock Event 2 (rising edge of ICLK2) the input signal becomes valid-low at the I input of both registers and is reflected on the IQ2 output of input-register 2 at time T<sub>IOCKIQ</sub> after Clock Event 2 (no change in this case).

- At time T<sub>IOSRCKI</sub> before Clock Event 9 the SR signal (configured as synchronous reset in this case) becomes valid-high resetting input-register 1 (IQ1) at time T<sub>IOCKIQ</sub> after Clock Event 9, and input-register 2 (IQ2) at time T<sub>IOCKIQ</sub> after Clock Event 10.

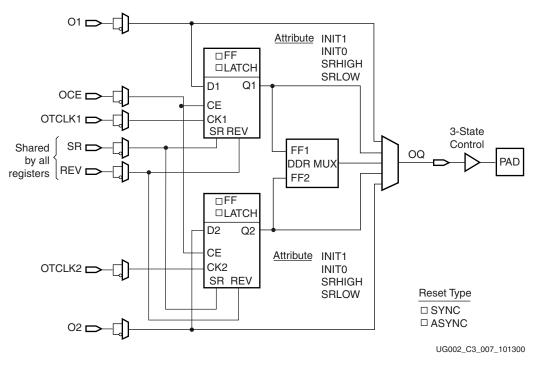

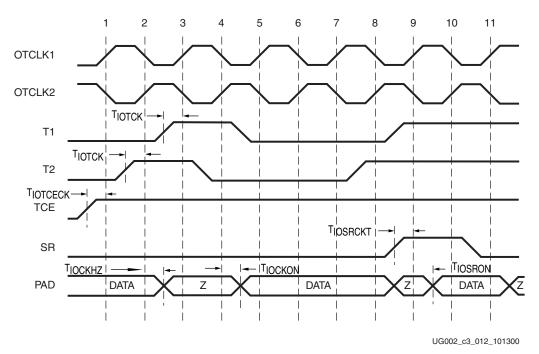

### IOB Output Timing Model and Parameters

Figure 1-16 illustrates IOB outputs.

Figure 1-16: Virtex-II IOB Output Diagram

#### **Timing Parameters**

| Parameter                                              | Function                                 | Control<br>Signal | Description                                                                                                       |  |  |

|--------------------------------------------------------|------------------------------------------|-------------------|-------------------------------------------------------------------------------------------------------------------|--|--|

| Propagation Delays                                     | Propagation Delays                       |                   |                                                                                                                   |  |  |

| T <sub>IOOP</sub>                                      |                                          |                   | Propagation delay from the O input of the IOB to the pad.                                                         |  |  |

| T <sub>IOOLP</sub>                                     |                                          |                   | Propagation delay from the O input of the IOB to the pad via transparent latch.                                   |  |  |

| Setup and Hold With F                                  | Respect to Clock at IOB                  | 0utput I          | Register                                                                                                          |  |  |

| $T_{xxCK}$ = Setup time (k<br>$T_{xxCKxx}$ = Hold time | pefore clock edge)<br>(after clock edge) |                   | The following descriptions are for setup times only.                                                              |  |  |

| T <sub>IOOCK</sub> /T <sub>IOCKO</sub>                 | O input                                  |                   | Time before the clock that data must be stable at the O input of the IOB Output Register.                         |  |  |

| T <sub>IOOCECK</sub> /T <sub>IOCKOCE</sub>             | OCE input                                |                   | Time before the clock that the Clock Enable signal must<br>be stable at the OCE input of the IOB Output Register. |  |  |

| T <sub>IOSRCKO</sub> /T <sub>IOCKOSR</sub>             | SR input (OFF)                           |                   | Time before the clock that the Set/Reset signal must be stable at the SR input of the IOB Output Register.        |  |  |

| Clock to Out                                           |                                          |                   |                                                                                                                   |  |  |

| T <sub>IOCKP</sub>                                     | Clock (CLK) to pad                       |                   | Time after the clock that the output data is stable at the pad.                                                   |  |  |

| Set/Reset Delays                                       |                                          |                   |                                                                                                                   |  |  |

| T <sub>IOSRP</sub>                                     | SR Input to pad (asynchronous)           |                   | Time after the Set/Reset input of the IOB is toggled that the pad reflects the set or reset.                      |  |  |

| T <sub>IOGSRQ</sub>                                    | GSR to pad                               |                   | Time after the Global Set/Reset is toggled that the pad reflects the set or reset.                                |  |  |

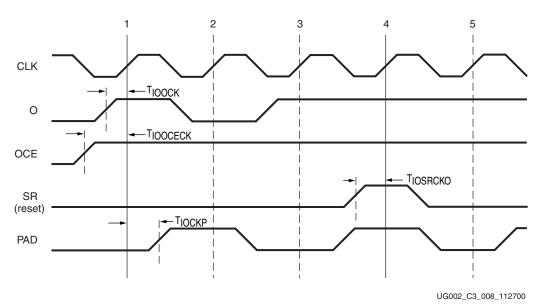

Figure 1-17: IOB Output Register Timing Diagram

#### **Clock Events**

- At time T<sub>IOOCECK</sub> before Clock Event 1, the output clock enable signal becomes validhigh at the OCE input of the output register, enabling the output register for incoming data.

- At time T<sub>IOOCK</sub> before Clock Event 1, the output signal becomes valid-high at the O input of the output register and is reflected on the pad at time T<sub>IOCKP</sub> after Clock Event 1.

- At time T<sub>IOSRCKO</sub> before Clock Event 4, the SR signal (configured as synchronous reset in this case) becomes valid-high, resetting the output register and reflected on the pad at time T<sub>IOCKP</sub> after Clock Event 4.

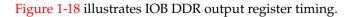

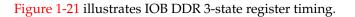

Figure 1-18: IOB DDR Output Register Timing Diagram

#### **Clock Events**

- At time T<sub>IOOCECK</sub> before Clock Event 1, the output clock enable signal becomes validhigh at the OCE input of both of the DDR output registers, enabling them for incoming data. Since the OCE signal is common to both DDR registers, care must be taken to toggle this signal between the rising edges of OTCLK1 and OTCLK2 as well as meeting the register setup-time relative to both clocks.

- At time T<sub>IOOCK</sub> before Clock Event 1 (rising edge of OTCLK1), the output signal O1 becomes valid-high at the O1 input of output register 1 and is reflected on the pad at time T<sub>IOCKP</sub> after Clock Event 1.

- At time T<sub>IOOCK</sub> before Clock Event 2 (rising edge of OTCLK2), the output signal O2 becomes valid-high at the O2 input of output register 2 and is reflected on the pad at time T<sub>IOCKP</sub> after Clock Event 2 (no change on the pad in this case).

- At time T<sub>IOSRCKO</sub> before Clock Event 9, the SR signal (configured as synchronous reset in this case) becomes valid-high, resetting output-register 1 (reflected on the pad at time T<sub>IOCKP</sub> after Clock Event 9) (no change in this case) and output-register 2 (reflected on the pad at time T<sub>IOCKP</sub> after Clock Event 10) (no change in this case).

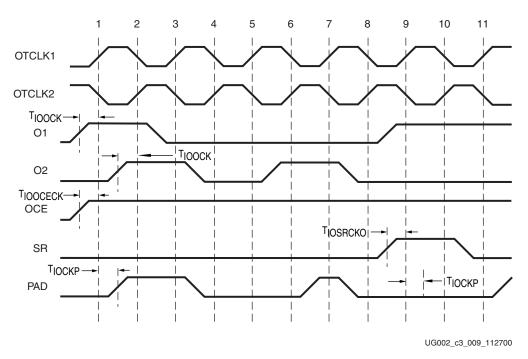

### IOB 3-State Timing Model and Parameters

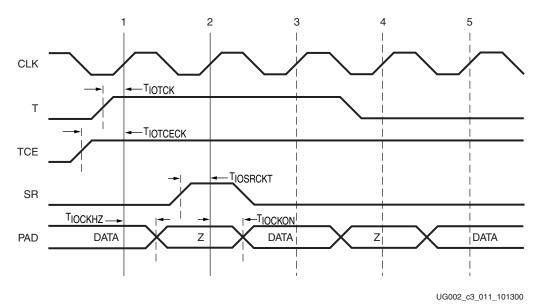

Figure 1-19 illustrates IOB 3-state timing

#### **Timing Parameters**

| Parameter                                                                                  | Function | Control<br>Signal | Description                                                                                                                   |

|--------------------------------------------------------------------------------------------|----------|-------------------|-------------------------------------------------------------------------------------------------------------------------------|

| Propagation Delays                                                                         |          |                   |                                                                                                                               |

| T <sub>IOTHZ</sub>                                                                         |          |                   | Time after T input of the IOB is toggled that the pad goes to high-impedance.                                                 |

| T <sub>IOTON</sub>                                                                         |          |                   | Time after the T input of the IOB is toggled that the pad goes from high-impedance to valid data.                             |

| T <sub>IOTLPHZ</sub>                                                                       |          |                   | Time after the T input of the IOB via transparent<br>latch is toggled that the pad goes to high-<br>impedance.                |

| T <sub>IOTLPON</sub>                                                                       |          |                   | Time after the T input of the IOB via transparent latch<br>is toggled that the pad goes from high-impedance to<br>valid data. |

| T <sub>GTS</sub>                                                                           |          |                   | Time after the Global 3-state signal is asserted that the pad goes to high-impedance.                                         |

| Setup and Hold With Respect to Clock at IOB 3-State Register                               |          |                   |                                                                                                                               |

| $T_{xxCK}$ = Setup time (before clock edge)<br>$T_{xxCKxx}$ = Hold time (after clock edge) |          |                   | The following descriptions are for setup times only.                                                                          |

| T <sub>IOTCK</sub> /T <sub>IOCKT</sub>                                                     | T input  |                   | Time before the clock that the signal must be stable<br>at the T input of the IOB 3-state Register.                           |

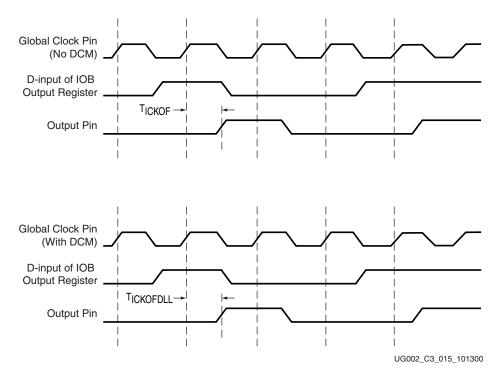

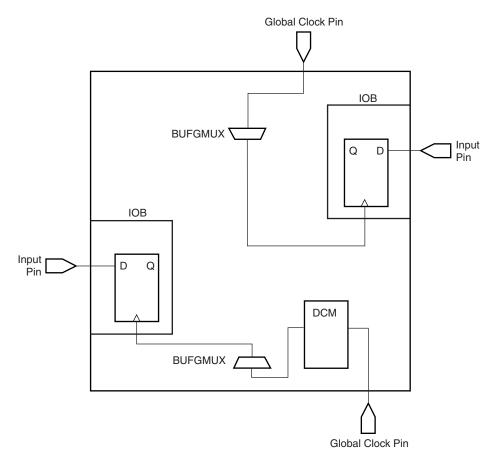

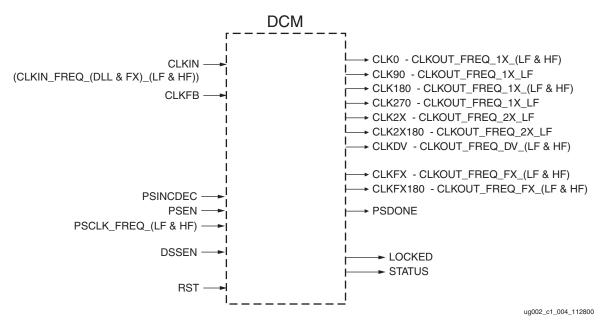

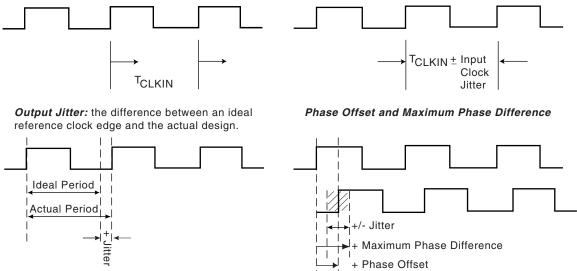

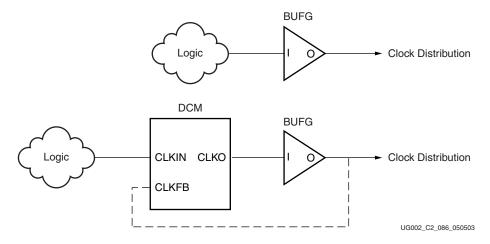

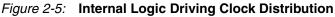

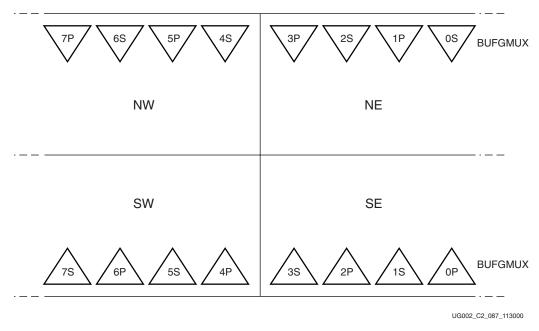

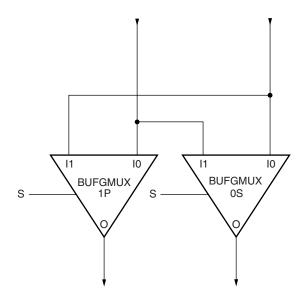

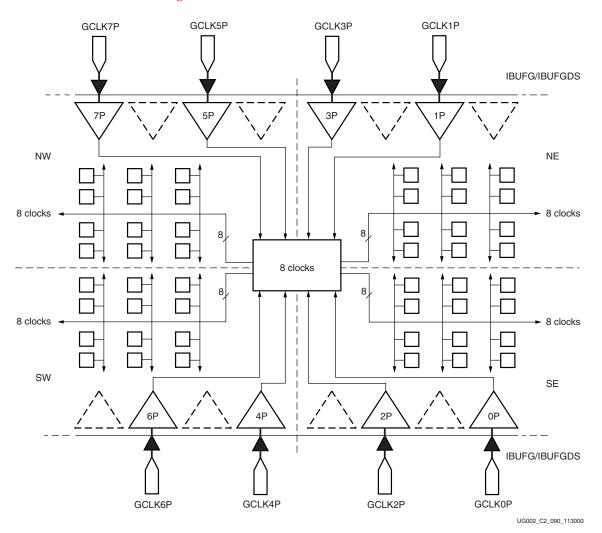

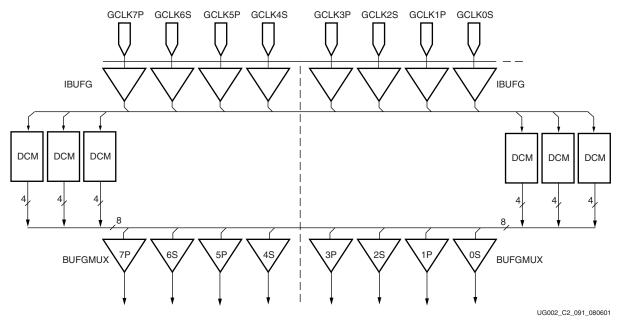

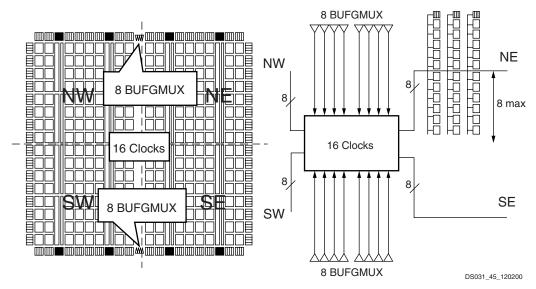

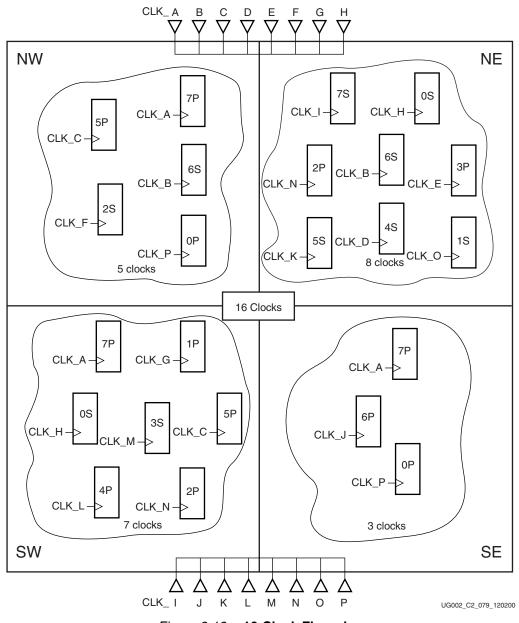

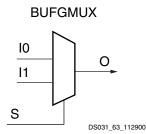

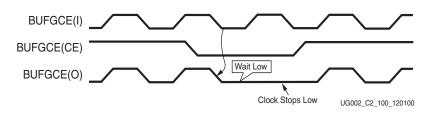

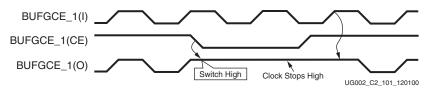

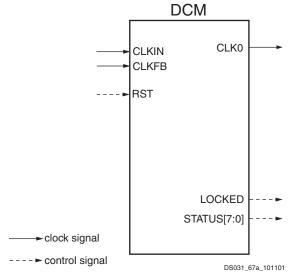

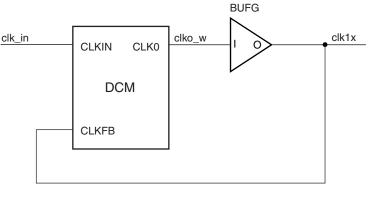

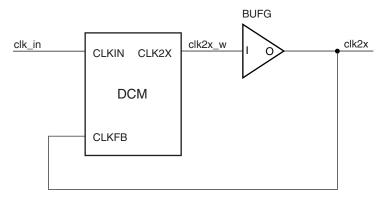

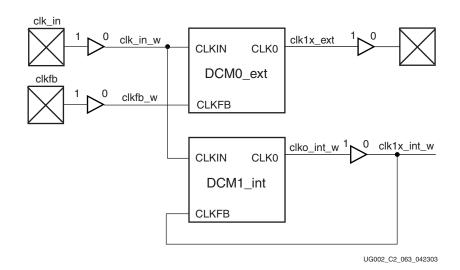

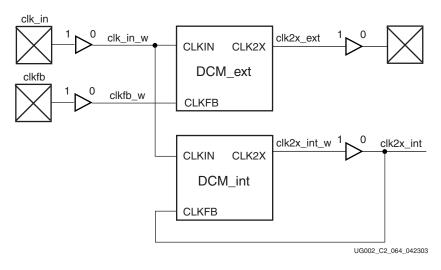

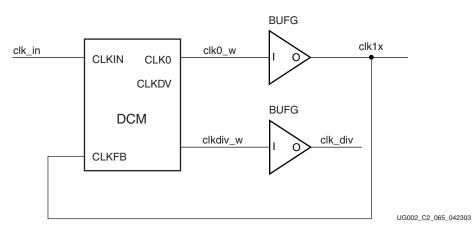

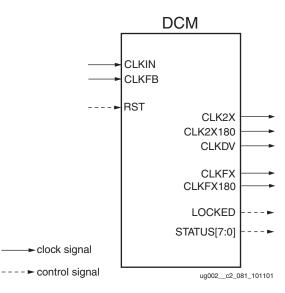

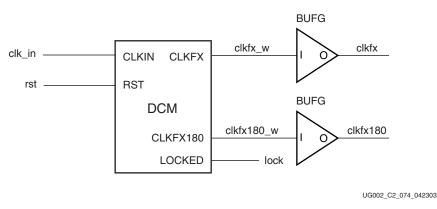

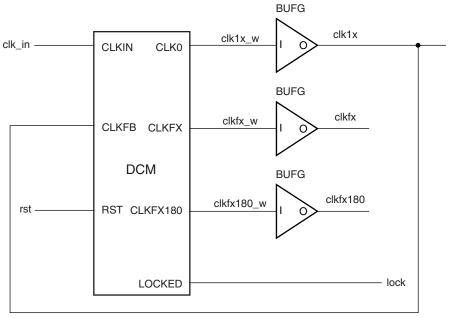

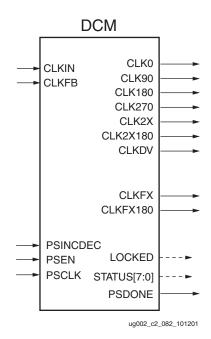

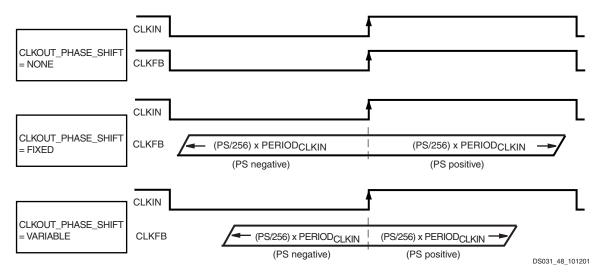

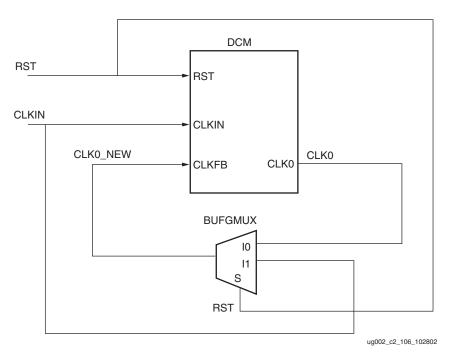

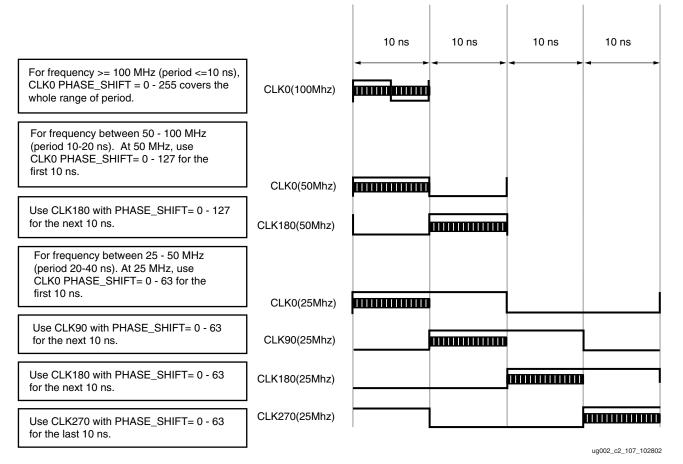

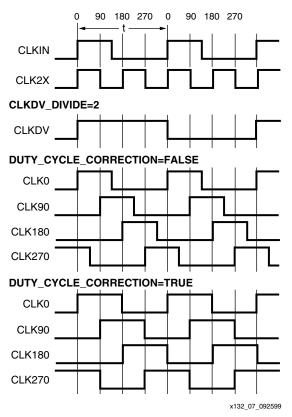

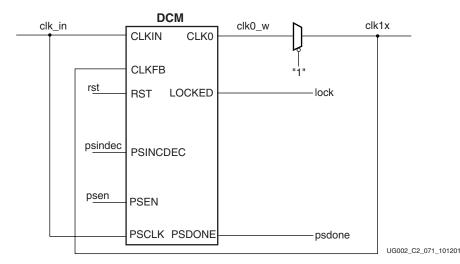

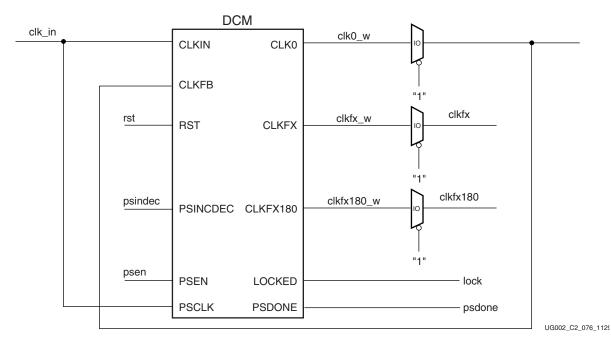

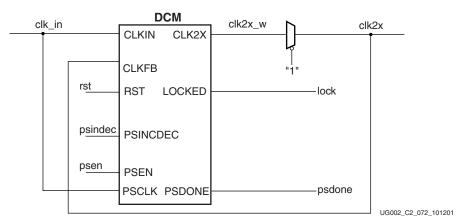

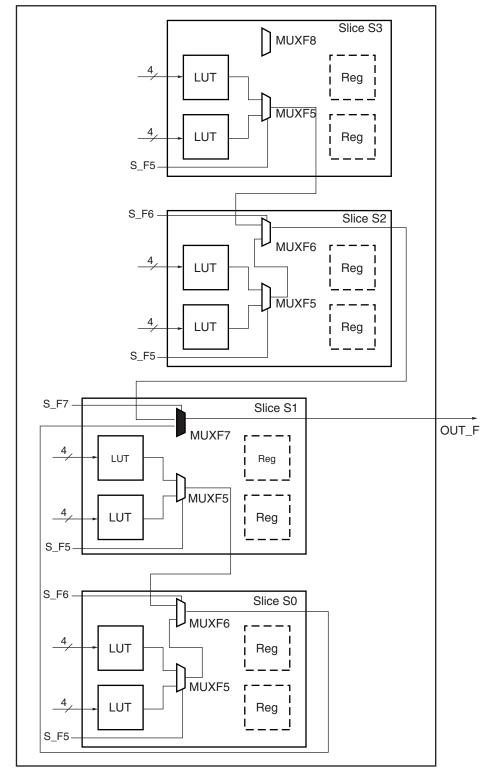

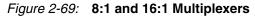

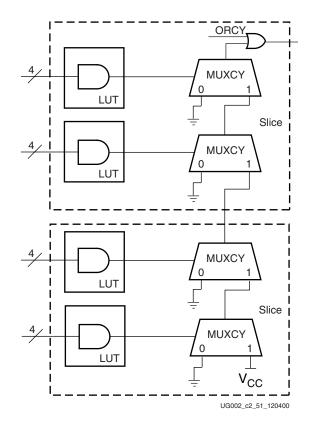

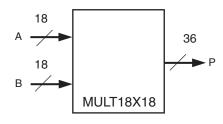

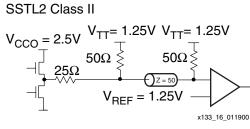

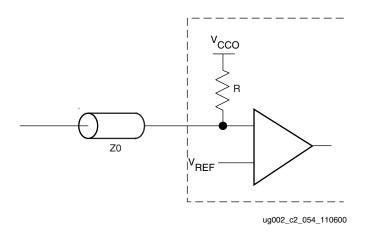

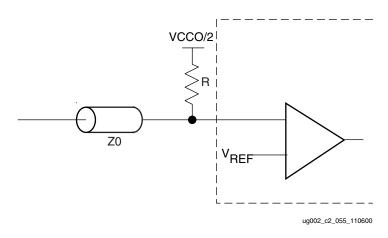

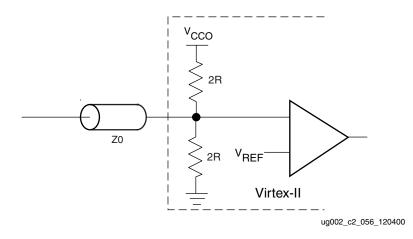

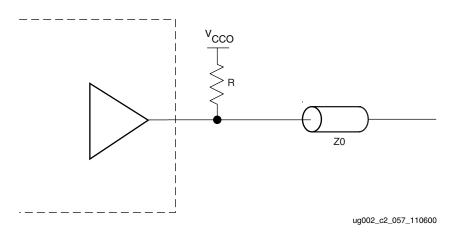

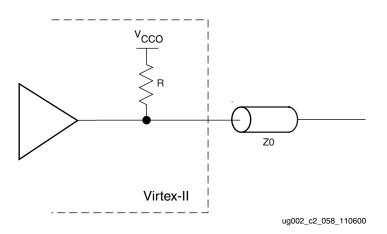

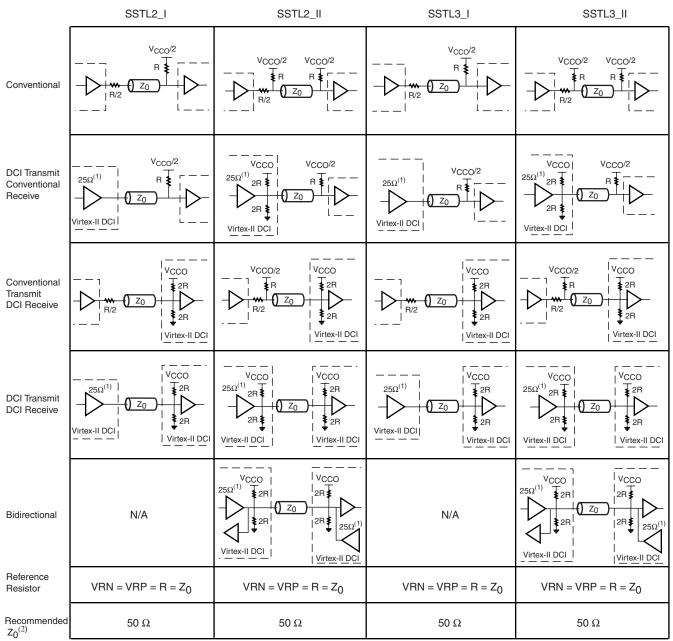

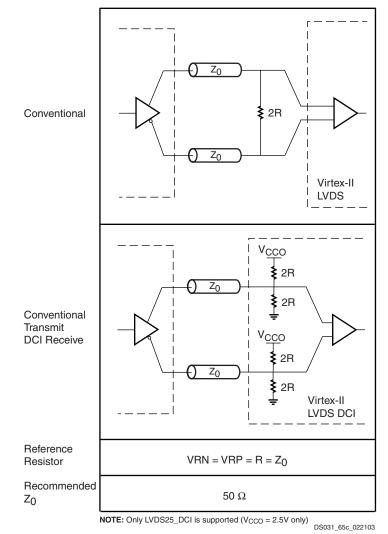

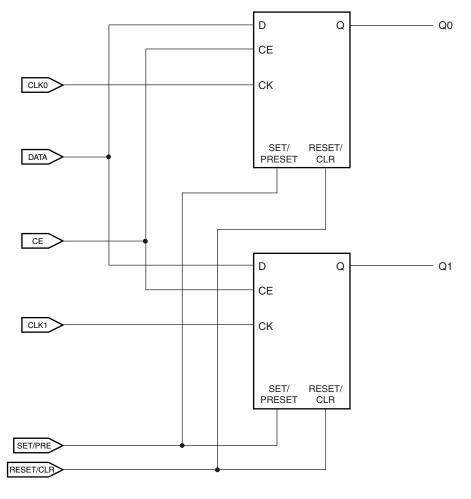

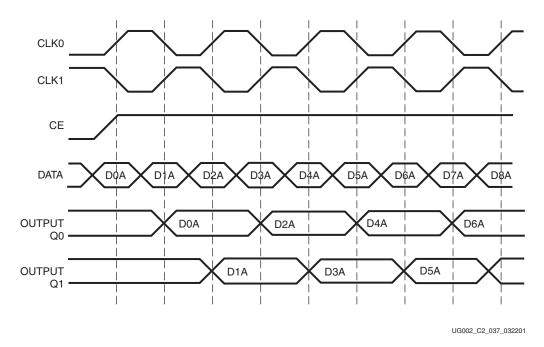

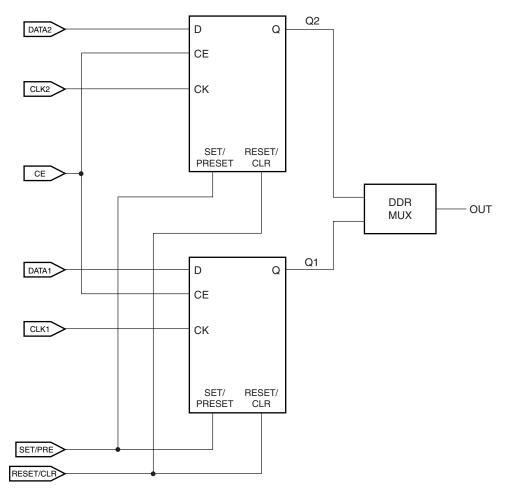

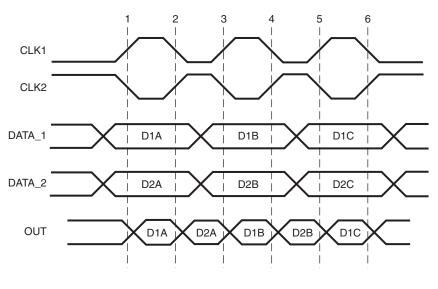

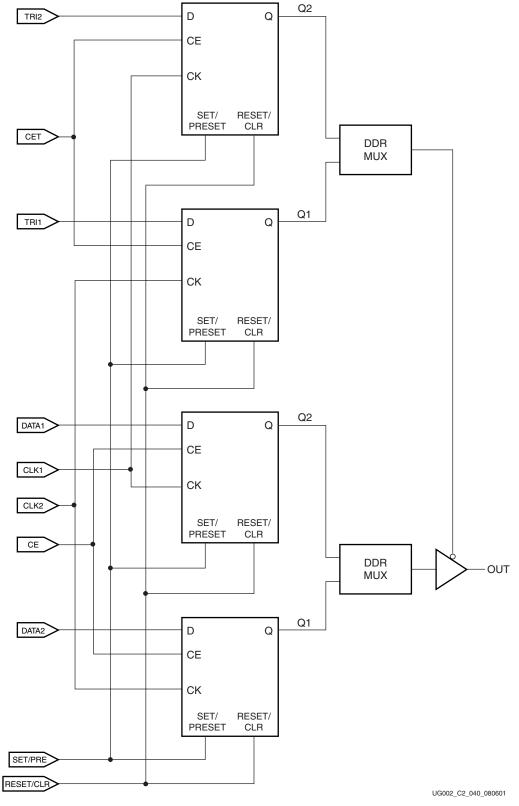

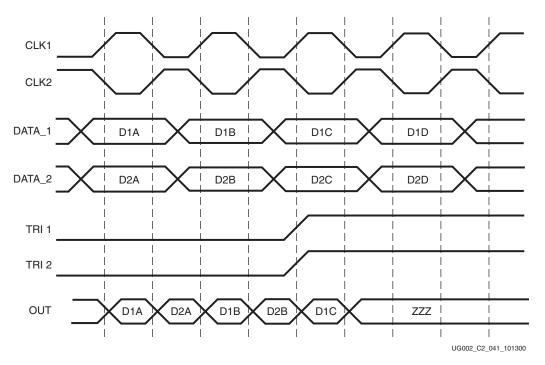

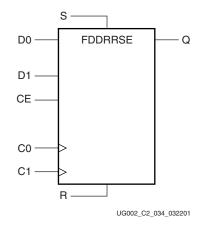

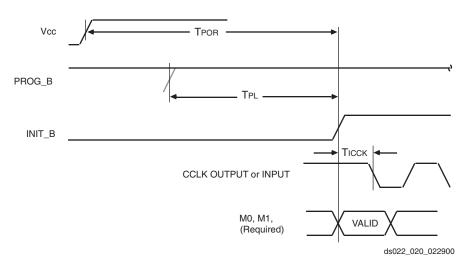

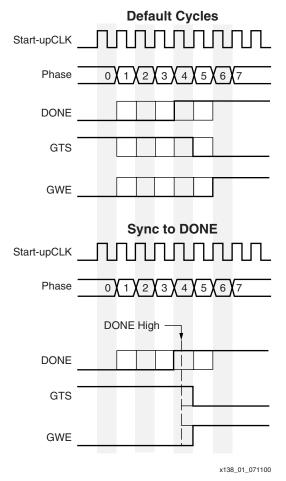

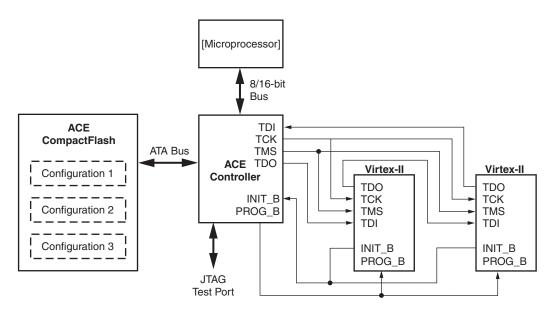

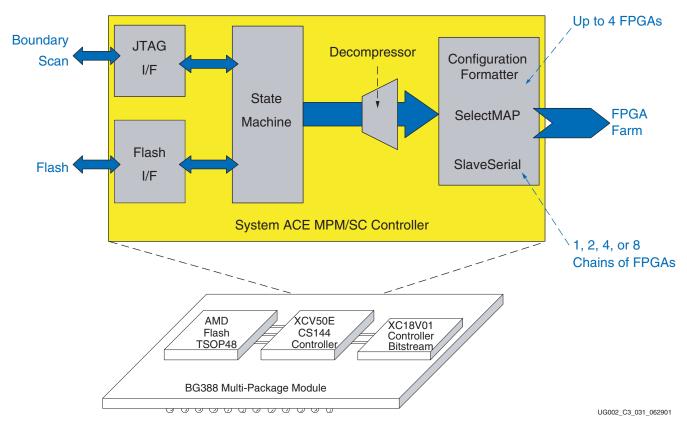

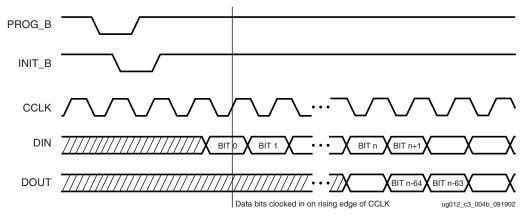

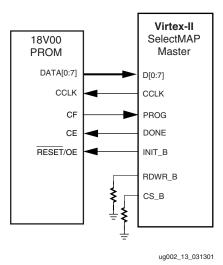

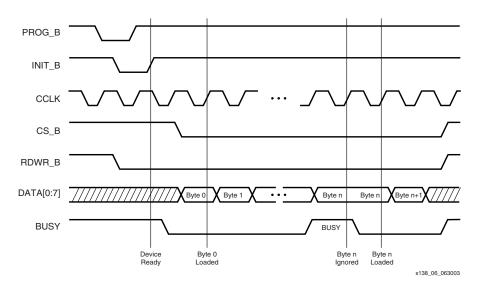

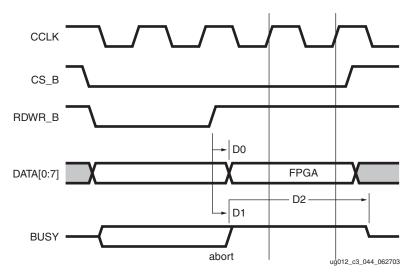

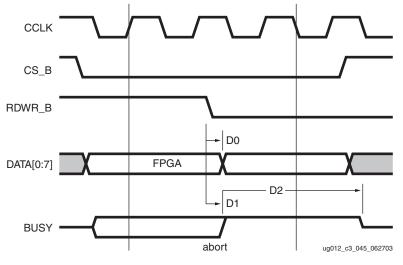

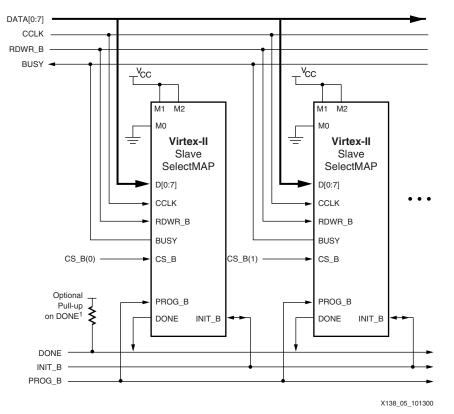

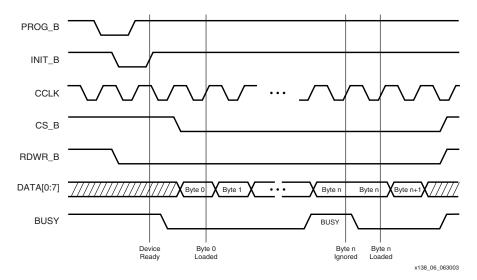

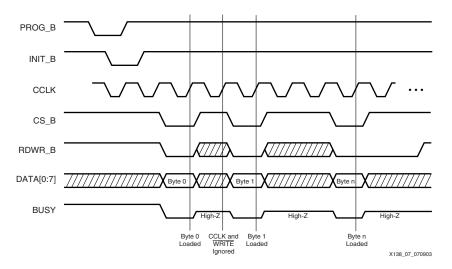

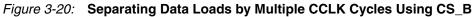

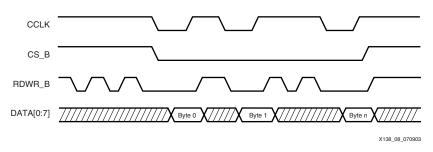

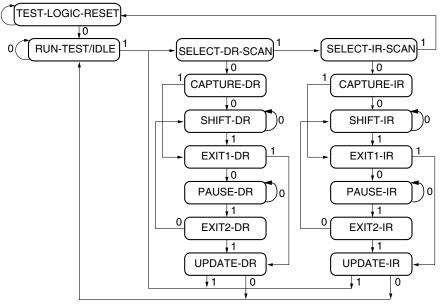

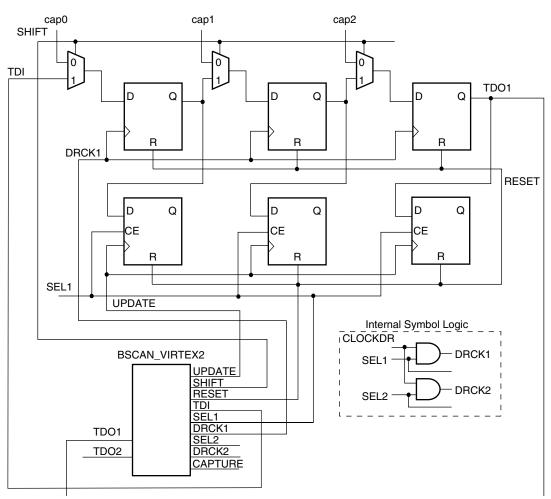

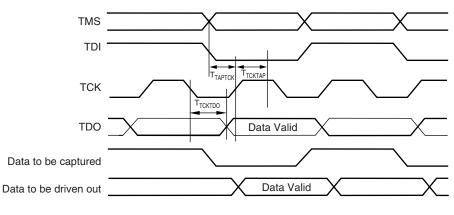

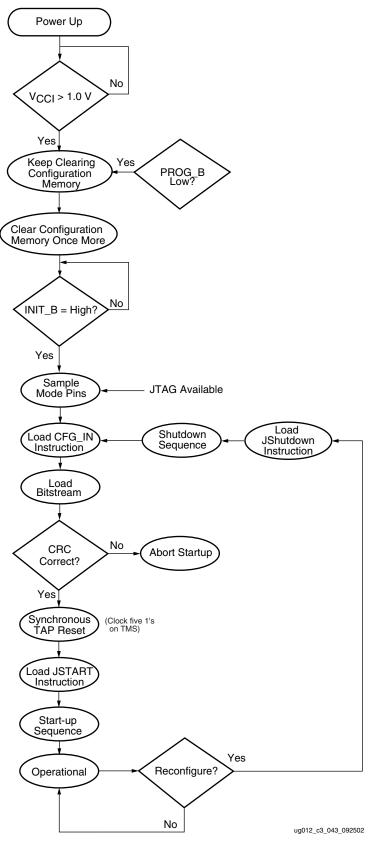

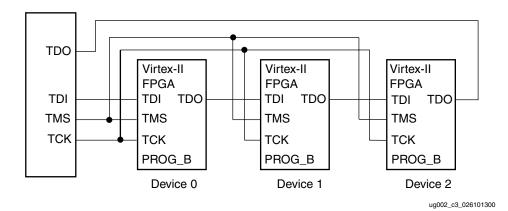

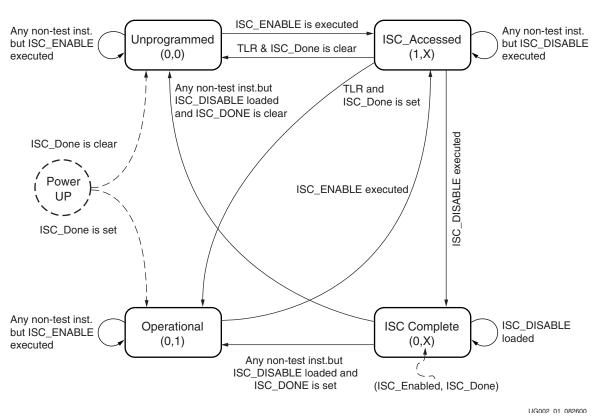

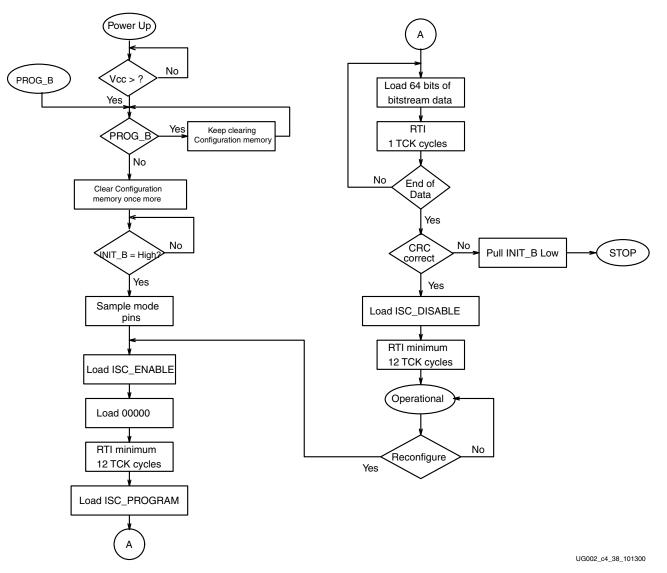

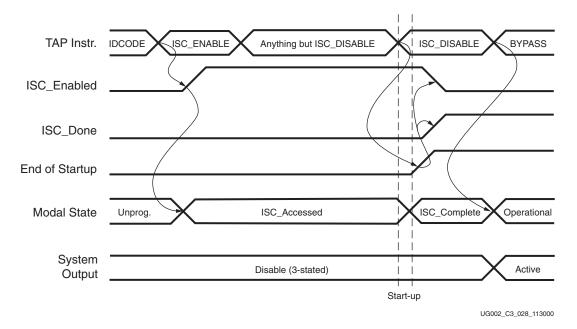

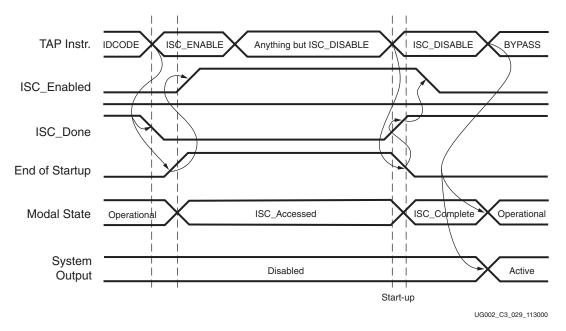

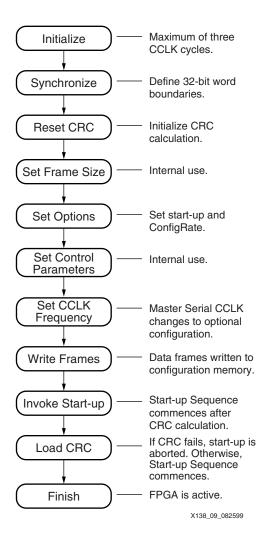

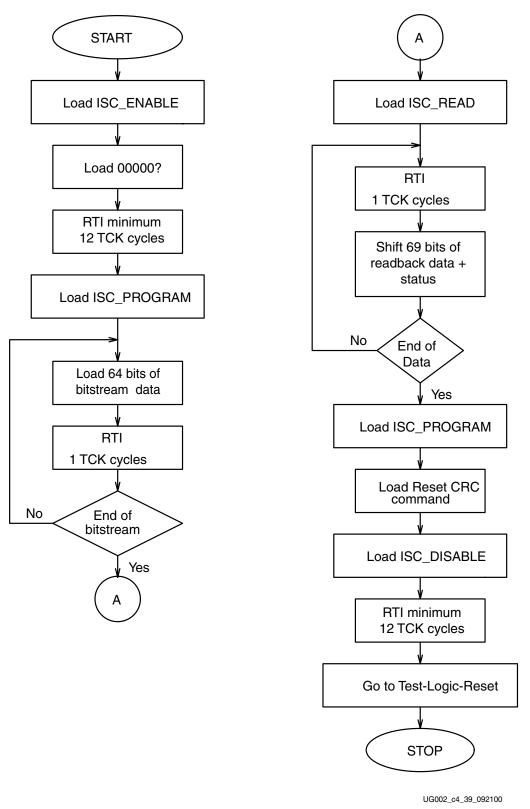

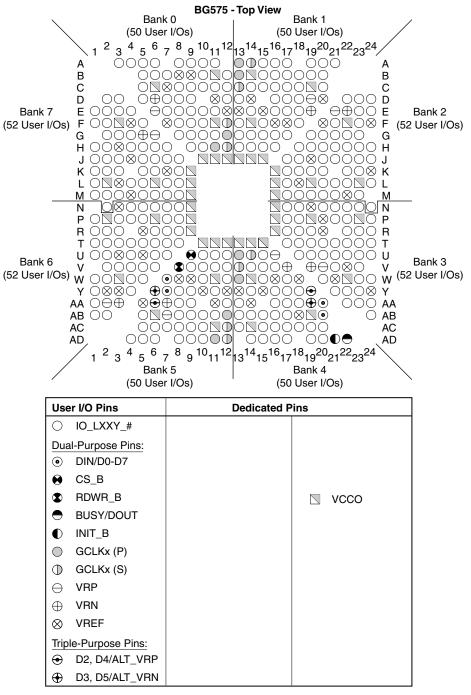

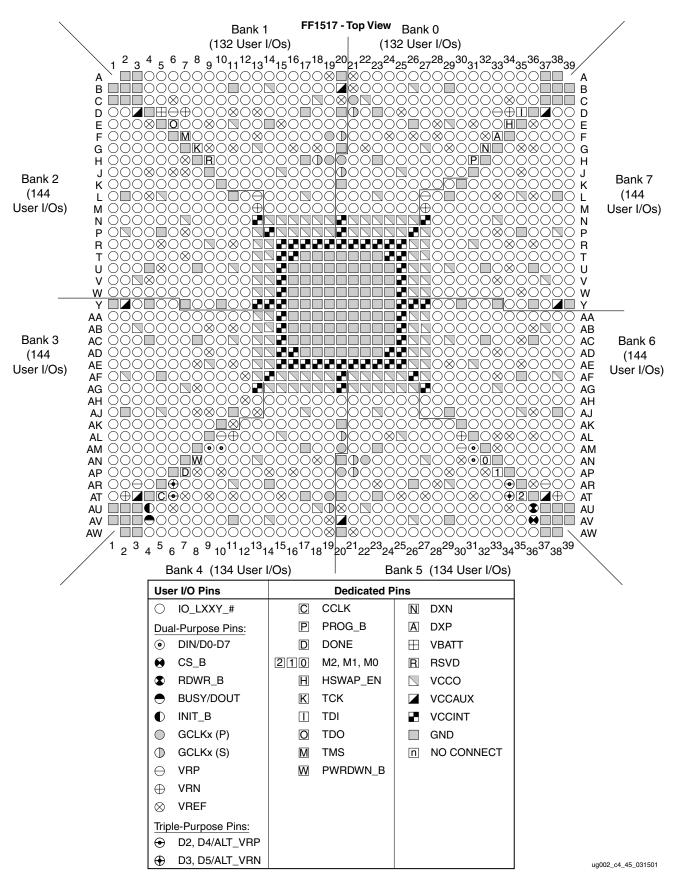

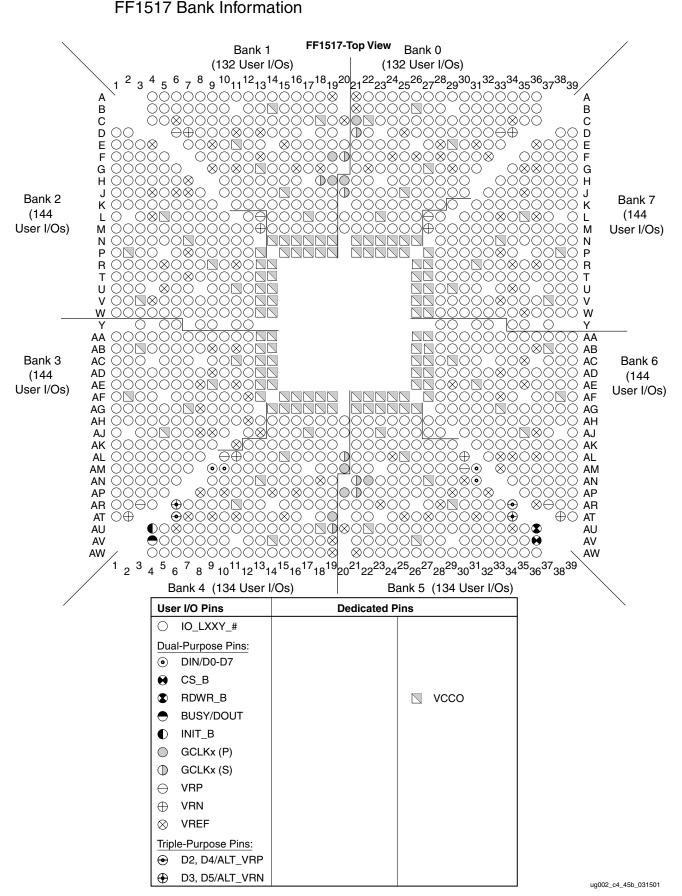

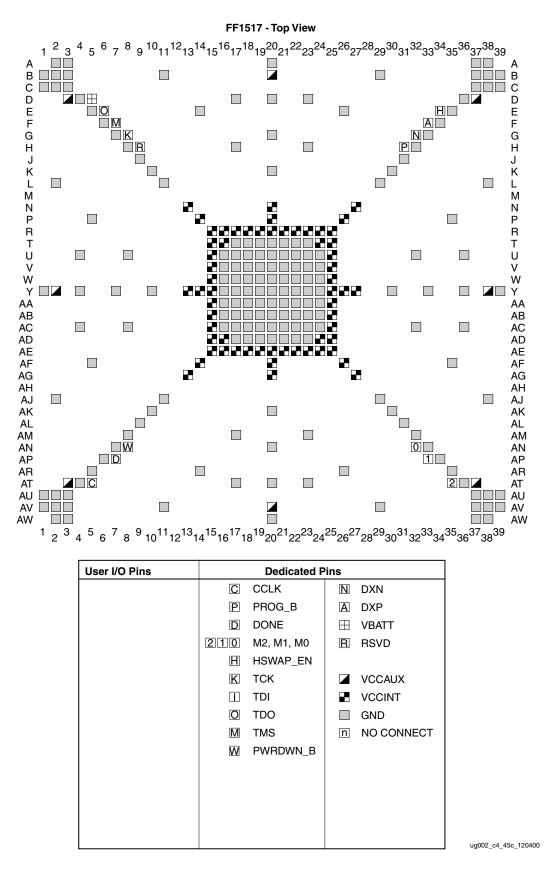

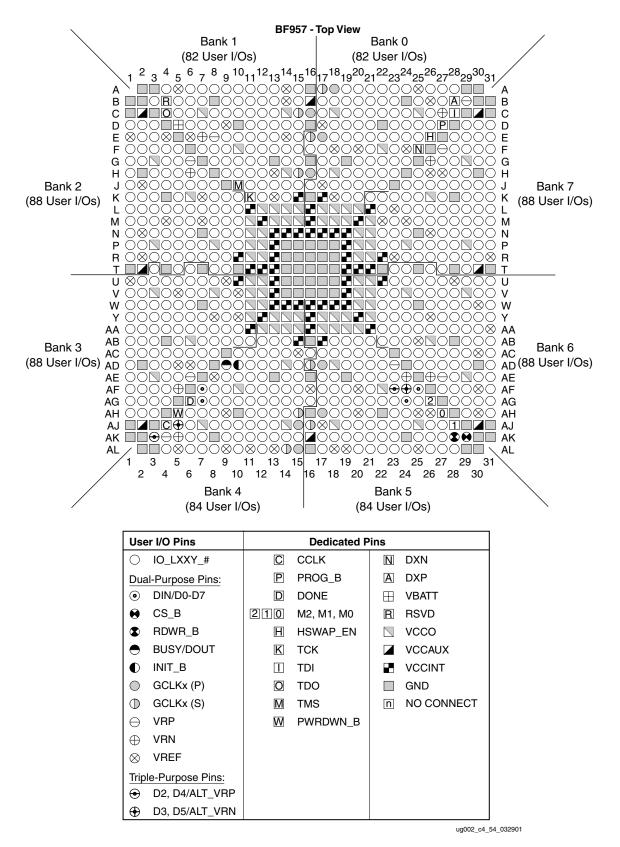

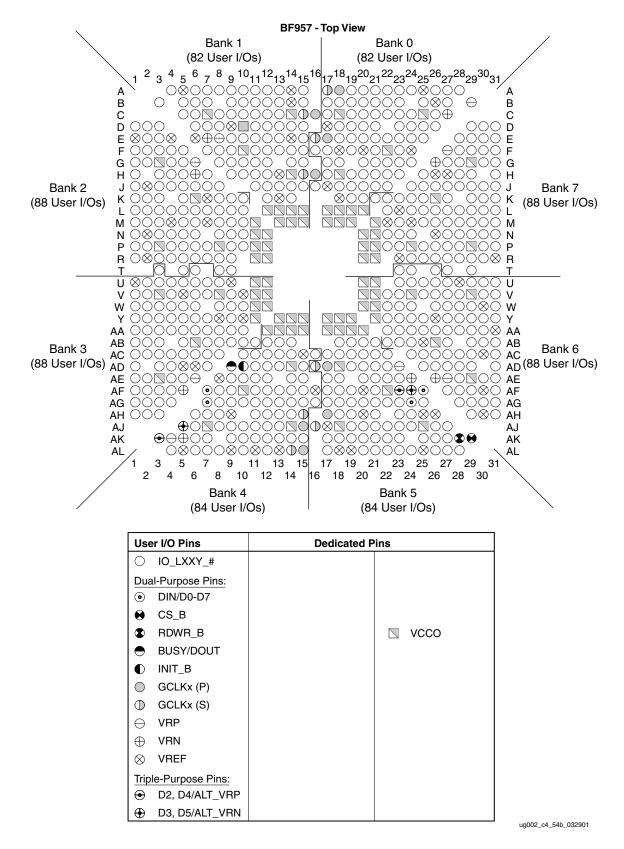

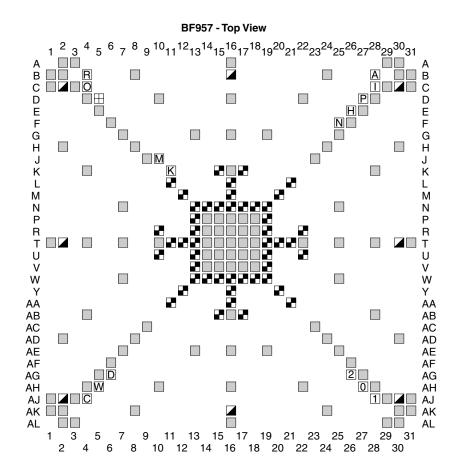

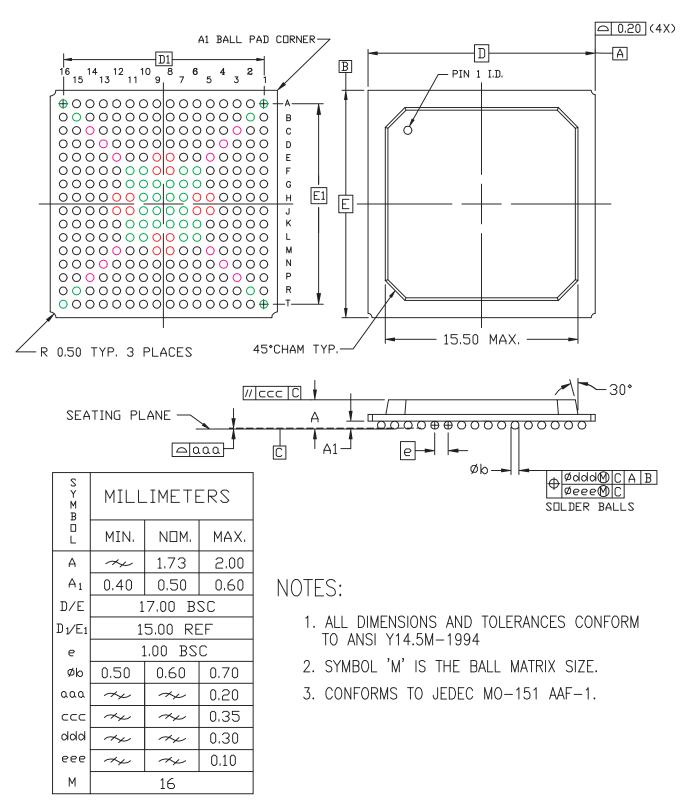

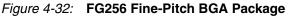

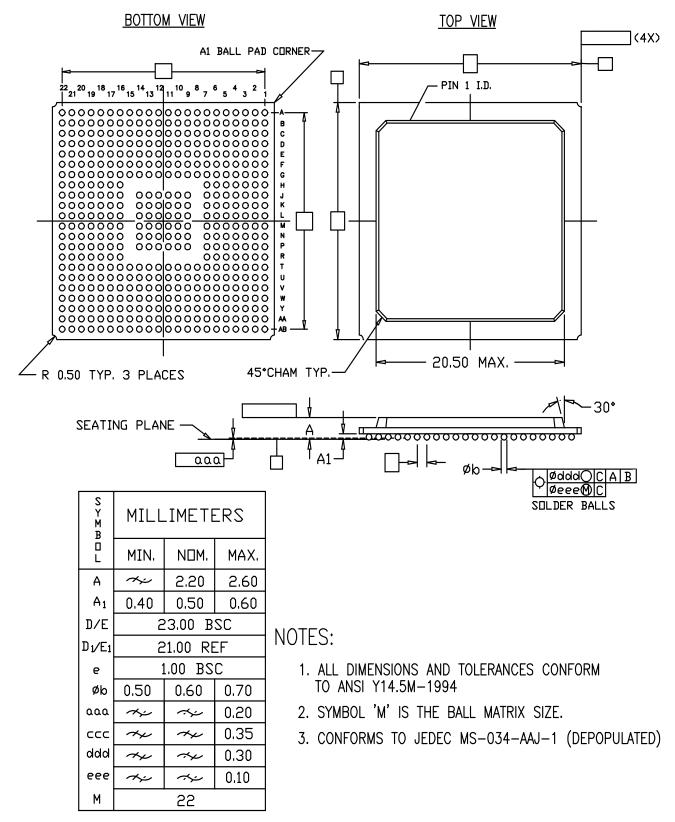

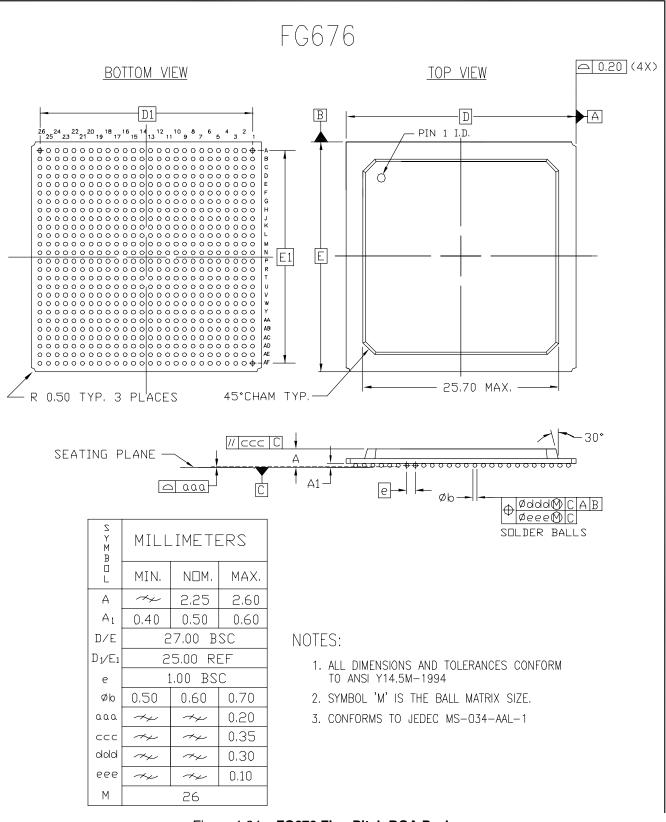

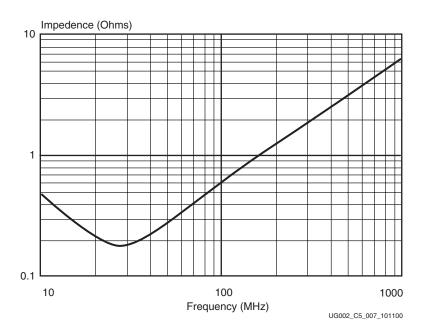

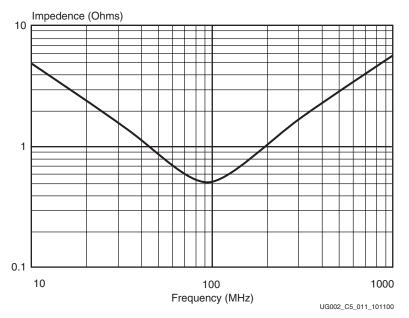

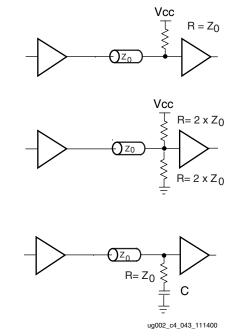

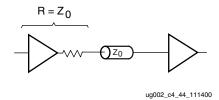

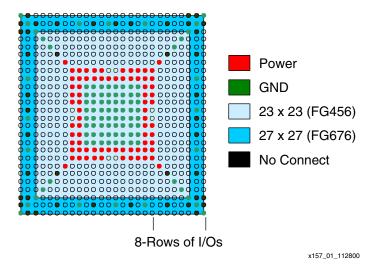

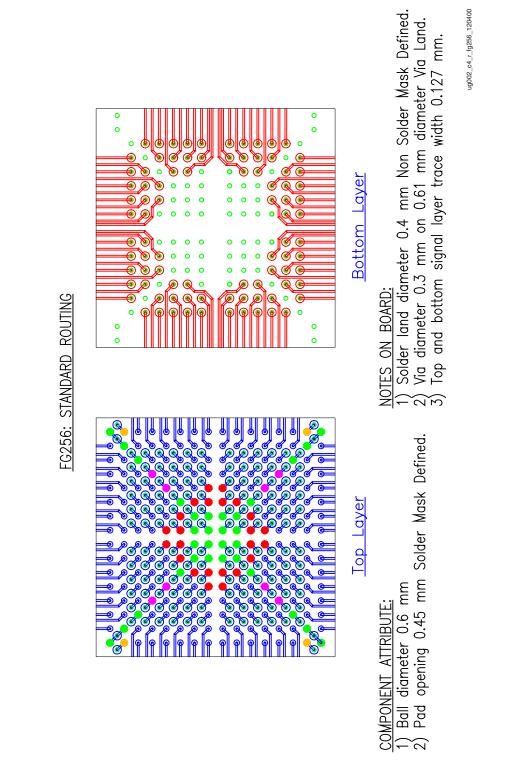

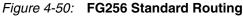

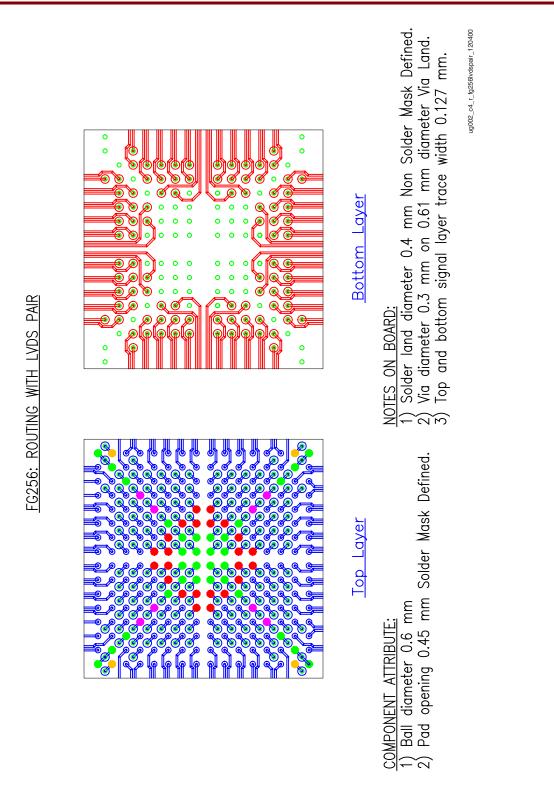

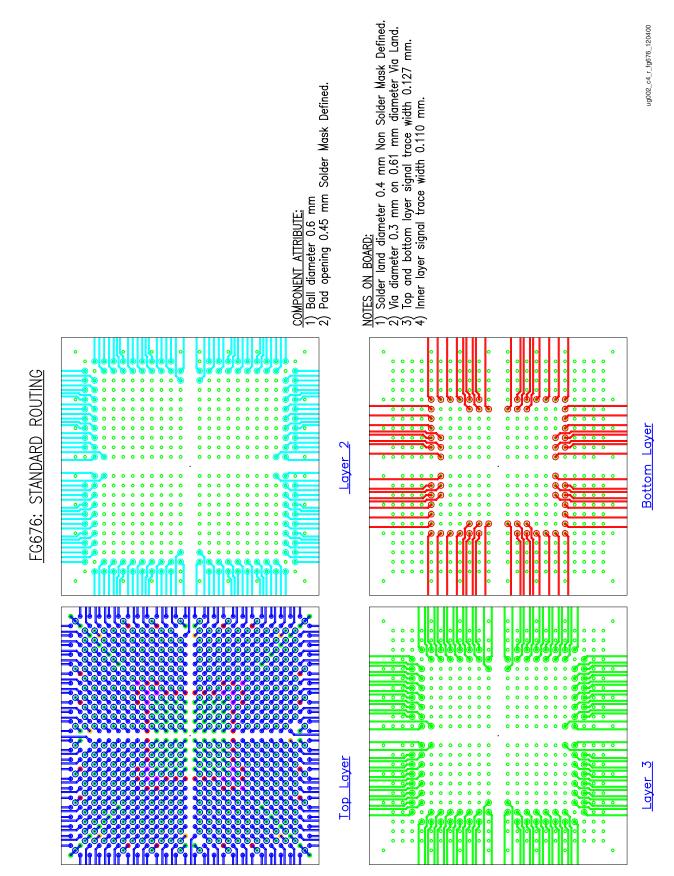

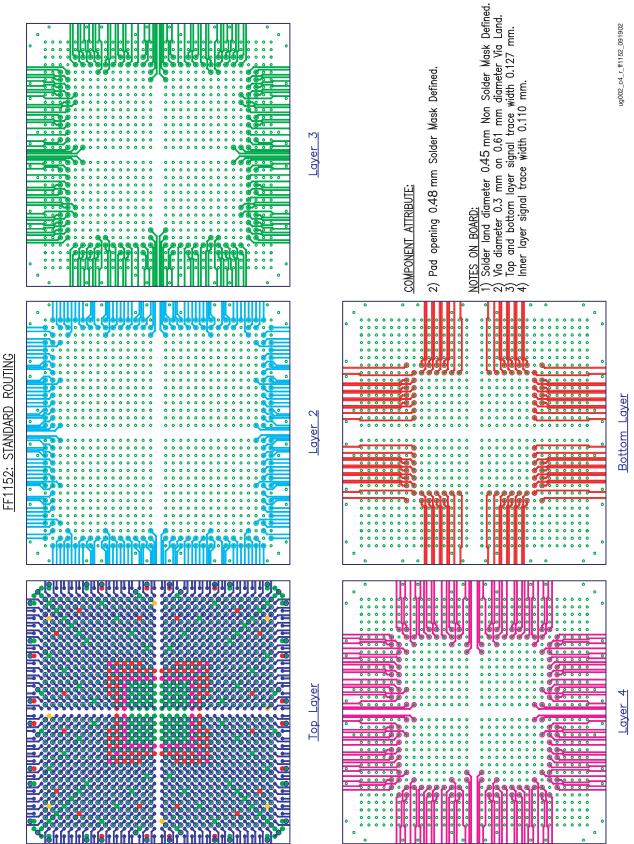

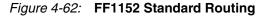

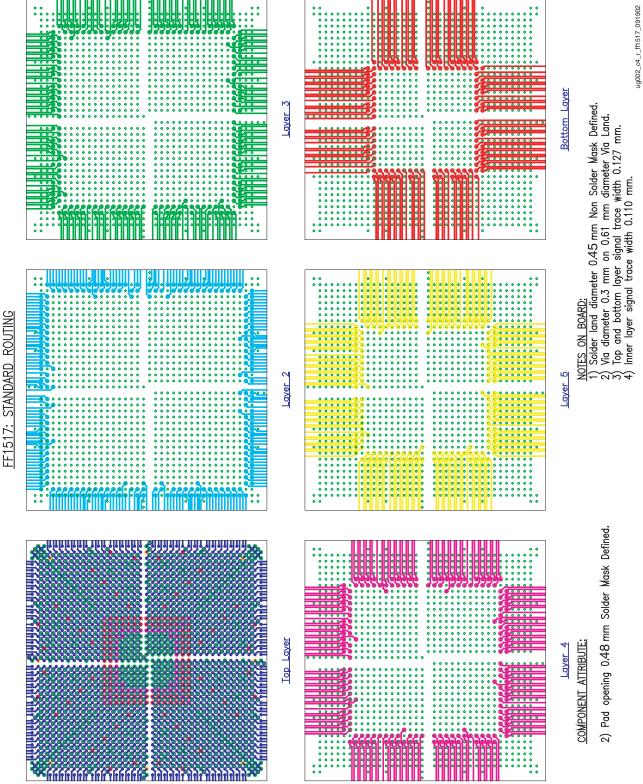

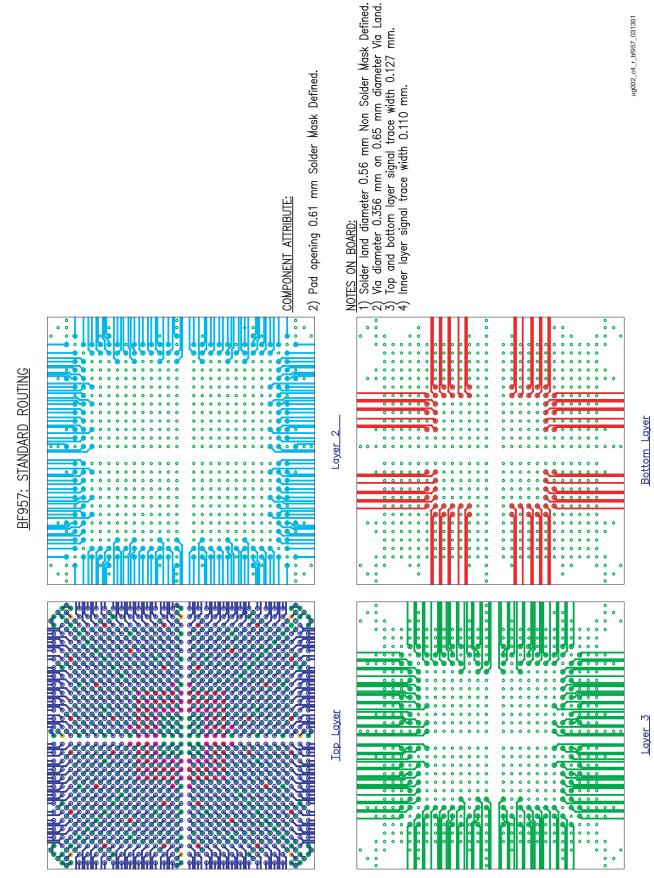

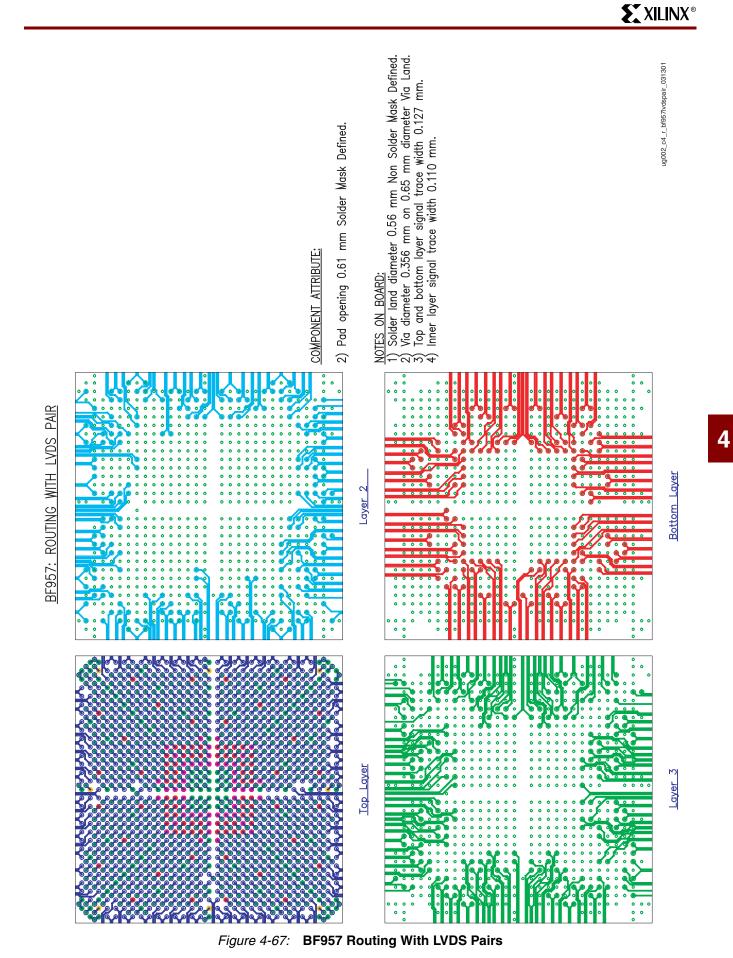

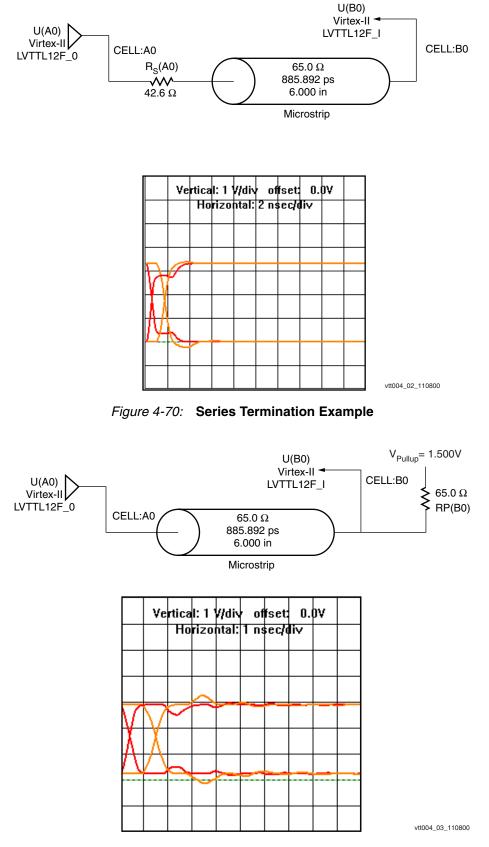

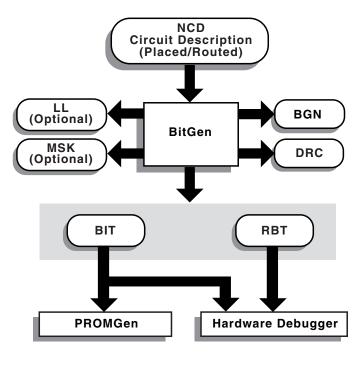

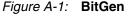

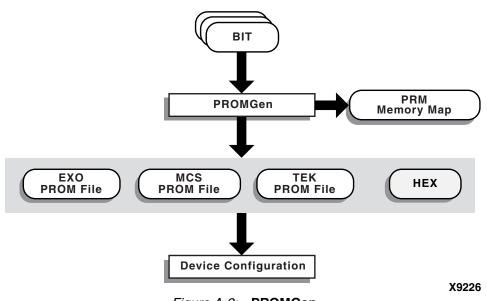

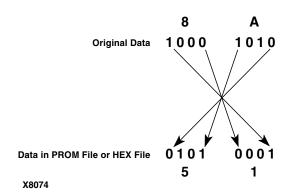

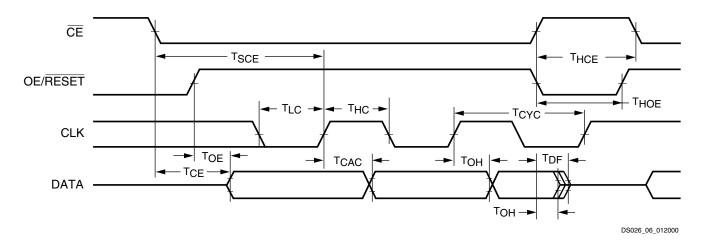

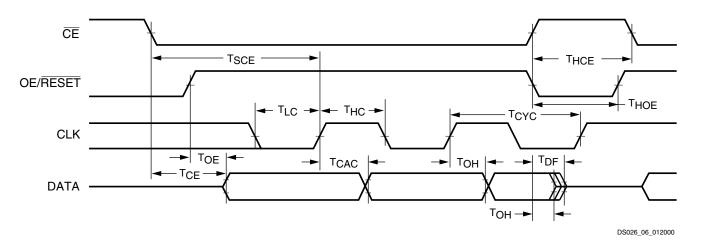

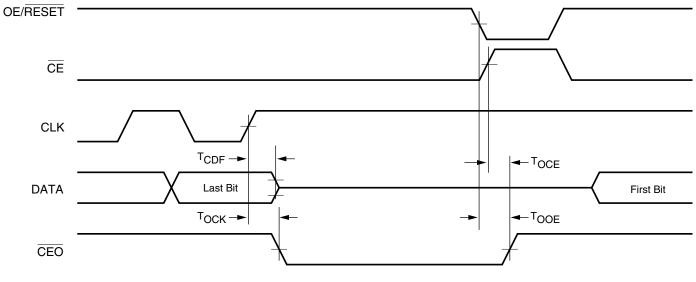

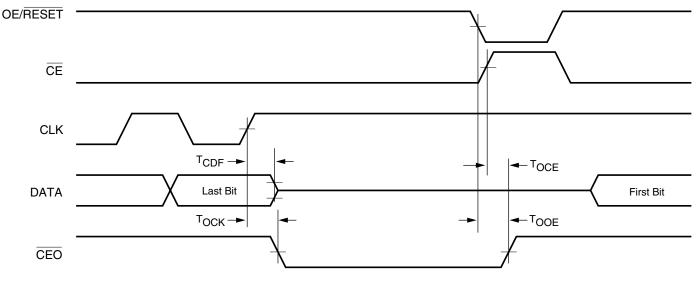

#