## Software/firmware activities @ MZ

- Working concurrently on support of existent hardware and pre-phase1 circuitry

- Software (Jan) and firmware (Uli) for JEM processors

- Software (Jan, Christian) and firmware (Christian, Patric, Stephan) for L1Topo

- Software for current systems is VME/HDMC based

- Mainz in charge of JEM module services / register maps ...

- Some contribution made to test vector generation in the not so recent past

- Probably just minor modifications required during LS1

- Software for L1Topo makes use of IPBus suite

- Need to write module services from scratch

- Register model, test vectors, GUIs, ..., ...

- L1Topo firmware under way

- Regina: physics / algo firmware coordination

- Stephan: algorithms

- Patric: infrastructure MGTs, real-time path before algos, including masking, error checking, play/spy, firmware based test vectors

- Christian: IPBus

- (Marek: readout)

# Software

Upgrade of JetProcessor pre-phase 1

- Using updated firmware register map from Stockholm

|              | Reserved              | ( ) | ( /   |            |                            |

|--------------|-----------------------|-----|-------|------------|----------------------------|

| Offset + 200 | RoI0:Threshold1/Size1 | 12  | 0x3FF | Read/Write |                            |

| Offset + 202 | RoI0:Threshold2/Size2 | 12  | 0x3FF | Read/Write | Bits Function              |

|              |                       | 12  | 0x3FF | Read/Write | Bito Function              |

| Offset + 214 | Rol3:Threshold1/Size1 | 12  | 0x3FF | Read/Write |                            |

| Offset + 216 | Rol3:Threshold2/Size2 | 12  | 0x3FF | Read/Write | Threshold / FCAL Threshold |

|              |                       | 12  | 0x3FF | Read/Write | 0 – 9 Threshold value      |

|              | Rol7:Threshold1/Size1 | 12  |       | Read/Write | 10 - 11 Cluster size       |

| Offset + 230 | RoI7:Threshold2/Size2 | 12  | 0x3FF | Read/Write | ] ••                       |

- Upgrade of EnergySumProcessor pre-phase 1

- Firmware not yet updated

- Updates to playback and spy memory

- changes in the module services, simulation and test vectors

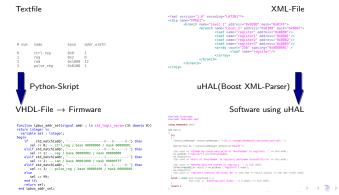

- Integration of IPBus sw/register model for L1Topo

- In cooperation with Christian and Murrough

- Trying to setup IPBus software and L1Calo package on a virtual machine in Mainz

- Write module services from scratch

- Register model, test vectors, ... to be done

L1Topo Module Control IPBus Protocol

Christian Kahra

Institut für Physik - ETAP Johannes Gutenberg-Universitaet Mainz

27. Juni 2013

Chr. Kahra (ETAP / IPh / JGU Mainz)

L1Topo Module Control

E ► E ∽QC 27.06.13 1/4

(日) (周) (三) (三)

#### L1Topo Module Control

- Communication between PC and Control-FPGA via Ethernet

- read-, write-, ... requests on module registers transacted by IPBus

- on prototype module the Processor FPGAs are connected with Control FPGA by 21 LVDS-pairs respectively

- these 21 LVDS-pairs are shared by Control, ROD and TTC

Standard approach: Every FPGA is IPBus-Endpoint

- sharing the Ethernet MAC via AXI4-Stream (David Sankey)

- AXI4 signals:

- receive side: mac\_rx\_data[7:0], mac\_rx\_error, mac\_rx\_last, mac\_rx\_valid

- transmit side: mac\_tx\_data[7:0], mac\_tx\_error, mac\_tx\_last, mac\_tx\_valid, mac\_tx\_ready

- every Endpoint sees whole traffic, discarding unwanted packets

- not possible on the prototype module because of limited bandwith

Alternative: Processor FPGAs are IPBus-Slaves

- IPBus-Slave on the Control FPGA represents Processor FPGA

- IPBus data-, address- and control- lines are serial connected to the Processor FPGA

- transaction is holded until acknowledge from the Processor FPGA arrives

▲日 ▶ ▲圖 ▶ ▲ 圖 ▶ ▲ 圖 ▶

#### IPBus address space

Description of the IPBus address space

- not coherent on firmware and software side

- a common XML description of the whole L1Topo firmware is in discussion

${\ }$  IPBus addresses would have to be part of this description Currently:

Chr. Kahra (ETAP / IPh / JGU Mainz)

L1Topo Module Control

### **Current MGT status**

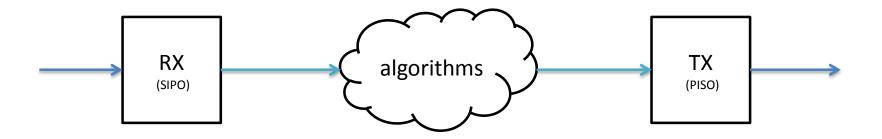

- Work on Top-Level-VHDL module with instantiated MGTs and connected algorithms

- C++ based instantiation and mapping of MGTs in development

- Currently also busy with BERT on AVAGO-MINIPOD mezzanine board based on Wojciechs format

# MET, HT and Meff

• MET= $\sqrt{E_x^2 + E_y^2}$

$\rightarrow$  implemented with CORDIC

| resource use [%] | latency [ns] |

|------------------|--------------|

| 0.11             | ~50          |

•  $HT=\Sigma p_T(jets)$  and  $Meff=\Sigma p_T(jets,MET)$  with 64 jet TOBs

| resource use [%] | latency [ns] |

|------------------|--------------|

| 0.44             | 23.1         |

• all implementations on xc7vx690tffg1927-2

# $oldsymbol{\phi}_{\mathsf{MET}}$

- $\phi_{\text{MET}} = \arctan\left(\frac{E_{\chi}}{E_{\chi}}\right)$

- CORDIC implementation (without format change)

| resource use [%] | latency [ns] |

|------------------|--------------|

| 0.12             | 17.2         |

- use sign of Ex and Ey to calculate quadrant,

- use relative size to calculate octant,

- use  $E_x > E_y$  threshold (with 7 thresholds) to get 0.1 granularity

| resource use [%] | DSP use [%] | latency [ns] |

|------------------|-------------|--------------|

| 0.06             | 0.19        | 12.5         |

## Transverse/Contratransverse Mass

•

$$M_T = \sqrt{2E_T MET(1 - \cos(\Delta \phi))}$$

$\rightarrow M_T^2 = 2E_T MET(1 - \cos(\Delta \phi))$

| resource use [%] | DSP use [%] | latency [ns] |

|------------------|-------------|--------------|

| 0.03             | 0.06        | 13.1         |

•

$$M_{CT} = \sqrt{2E_T MET(1 + \cos(\Delta \phi))}$$

$\rightarrow M_{CT}^2 = 2E_T MET(1 + \cos(\Delta \phi))$

| resource use [%] | DSP use [%] | latency [ns] |

|------------------|-------------|--------------|

| 0.02             | 0.06        | 12.5         |

# Testimplementation with multiple algorithms

- maximum number of cluster TOBs

- with sorting 6

- with selection 6

- maximum number of jet TOBs

- with sorting 10

- with selection 10

- whole algorithm module has a latency of 3 BC

- currently reworking selection algorithm