# jFEX / L1Topo

- Status & Plans (medium term) -

Uli / MZ Slides by Julio, Katharina

# jFEX Status

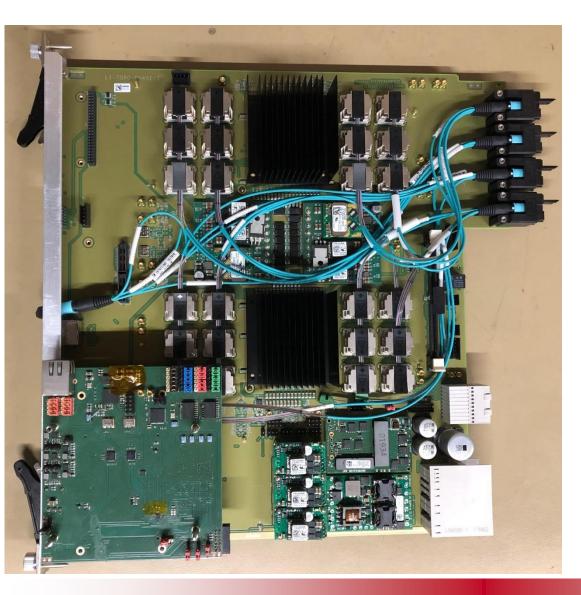

- Pre-Production module

- Ordered full set of production PCBs (10 pieces), because of no significant cost impact

- Delay at PCB manufacturer, because of long lead time of PCB material

- PCBs at assembly company

- Assembly (SMT) being worked on

- Some components (THT) were difficult to procure, going out to assembly company today. THT components last assembly step anyway.

- Expect to have the board in Mainz early December

- Tests of Pre-Production board will be only verification along the lines of prototype tests

- No design changes wrt Final Prototype

- All components for final production in hands, therefore NO further DELAYS expected at next stage...

- Firmware

- Ongoing integration of infrastructure firmware (MGTs, board control, IOs and etc.) and algorithms

# Hardware Availability (Status/Plan)

- jFEX First Prototype Currently at CERN (STF)

- Equipped with one UltraScale FPGA

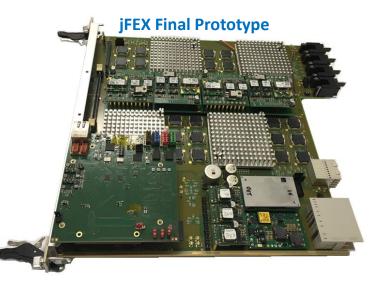

- jFEX Final Prototype Currently at CERN (STF)

- Equipped with four UltraScale+ FPGAs

- jFEX Pre-Production Module Available from mid December 2018 onwards

- Pre-Production module will be used as a spare, once production modules have been built

- jFEX Production Modules Available from May 2019 onwards

- 9 (+ 1) modules

- 6 to be installed

- 3 (+ 1) spares

## Module tests

#### Final Prototype = Pre-Production Module = Production Module

- No hardware changes are expected from prototype through production modules

- Rigorous tests of first and final prototype taken place

- in Mainz (power-up, local loopback IBERT, power drain / thermal tests)

- In Heidelberg (TREX link tests, IBERT, in September)

- At STF (see next slide)

- Final Prototype available for system-level tests (integration tests)

- Pre-Production from December/ January

# Surface Test Facility

- Setup ready for tests with jFEX First Prototype and FTM since July

- Tests of optical links, TTC clock reception, IPBus and etc. were performed

- jFEX Final Prototype was shipped to CERN along with L1Topo prototype. Initial tests done.

- Joint test week for jFEX final prototype

Pre-Production and L1Topo with software/firmware integration in week Dec. 10

- Expecting to run formatted data jFEX→L1Topo

#### jFEX setup on the STF

# Next tests @ STF

#### System-level tests with all interfacing modules

- jFEX and L1Topo (prototype) meant to be at the STF long-term, joint tests possible over long periods . Starting wk. Dec. 10.

- IPbus being exercised during all tests

- DCS make use of it as it becomes available. Initial steps (test wk. Dec. 10):

- Read some environmental conditions via IPbus

- Start using IPMC for reading some basic I2C sensor data

- Initial readout tests with Hub/ROD planned for wk. Dec. 10 (Marek)

- Start LATOME → jFEX integration asap

- Need to discuss LATOME availability and required tests pre-PRR

#### NEED TO SCHEDULE TESTS WITH THE RESPECTIVE MODULES

## Production modules

- Expect to get through volume production quickly: No more delays due to component procurement issues

- As soon as we get the go-ahead, assembly can start

- Bruno expecting to complete ~ 2 modules per week

- Going through established test routine in Mainz won't take much time

- → expect the production modules to populate the STF quickly once we are through the PRR

#### AGAIN, NEED TO SCHEDULE TESTS

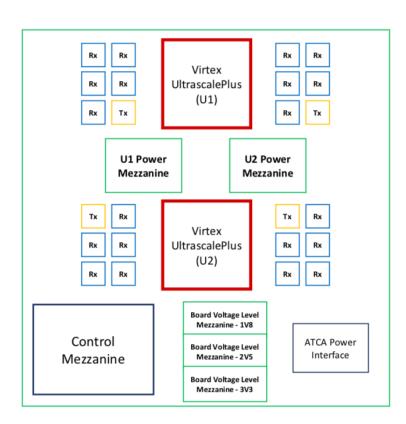

- L1Topo based on jFEX hardware-wise

- 2 Ultrascale+ FPGAs per module

- 118 input fibres per processor FPGA (6.4, 11.2 and 12.8 Gb/s)

- 24 output fibres per processor FPGA (6.4 and 12.8 Gb/s)

- Inter-FPGA connectivity 64 Gb/s (latency!)

- Control on mezzanine

- Electrical and optical output to CTP

- 3 ATCA modules at Point 1

Prototype at CERN since end of October `18

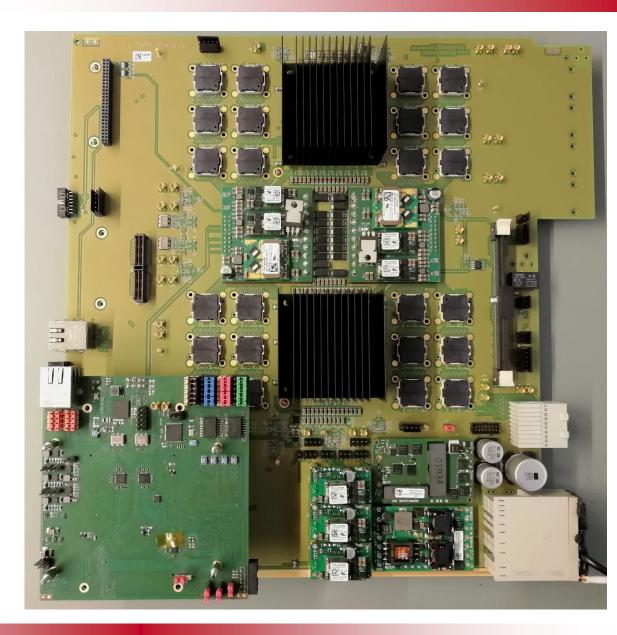

# L1Topo prototype

In Mainz...

... initial smoke tests...

..without optics...

# Fibred... and at STF finally ...

- Preliminary design review took place in November 2017

- https://indico.cern.ch/event/676491/

- L1Topo currently at STF for testing together with the jFEX final prototype

- Final design review scheduled on January 23<sup>rd</sup> 2019

- Firmware

- Ongoing integration of infrastructure firmware (MGTs, board control, IOs and etc.) and algorithms

#### **Final Prototype = Pre-Production Module = Production Module**

- No hardware changes are foreseen from prototype to production module

- Initial integration tests with other systems can start at anytime with prototype

- Combined tests with jFEX already ongoing

- Scheduled dedicated test week for software and firmware mid of December with all experts present

- Combined tests with eFEX, gFEX, MUCTPI and CTP still need to be scheduled

- Setup ready for tests with L1Topo prototype, jFEX and FTM since beginning of November

- Tests of optical links, TTC clock reception, IPBus and etc. were performed

- Aim to test and validate full module functionality at STF except:

- Concurrent operation of all FEXes (all modules), MUCTPI and CTP

- Validation of input mapping

- Final timing calibration

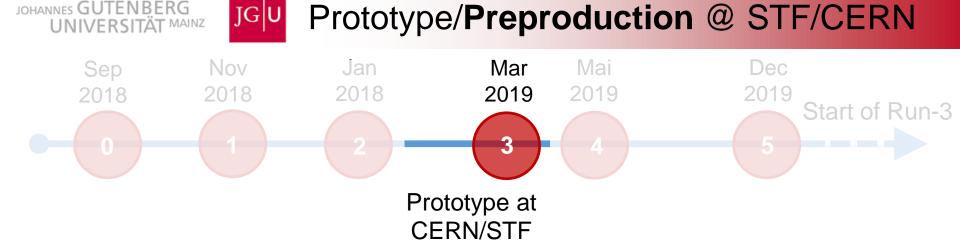

## Major Milestones for L1Topo towards Installation

- Prototype in Mainz

- Prototype available at CERN/STF

- 2 Final Design Review

- Production Readiness Review

- Production modules available at CERN/STF

- 5 Installation in USA15

# Prototype at STF/CERN

Prototype Prototype at in Mainz CERN/STF

- Initial validation tests of prototype has been done in Mainz

- Smoke tests and basic validation of board optical/electronical links

- Prototype available at CERN since end of October 2018

- Validation of prototype currently ongoing at STF/CERN

- Integrated test with FTM and jFEX

- Validation of all input and output links concurrently

- TTC and ROD links

- Latency measurement

- I2C/IPBus/OPC/DCS tests

- Power tests with all interfaces fully active

- FDR scheduled for January 23rd 2019

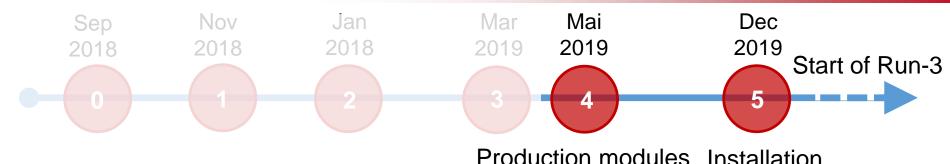

**Final Prototype = Pre-Production Module = Production Module**

- Continue validation of prototype/pre-production module at STF/CERN

- Integrated test with FTM, FEXes, MUCTPI and CTP

- Aim for PRR end of March 2019

### **Production** modules at STF/CERN

at CERN/STF

- Initial acceptance tests will be done in Mainz

- Smoke tests and basic validation of board optical/electronical links

- Production modules will be available at CERN Mai 2019

- Finalization of acceptance tests on ATCA crate in the STF

- Full slice test with all FEXes via Topo to CTP

- Integration with "L1Calo STF partition"

- Final installation steps planned for December 2019 to maximize time for pre-commissioning at STF

- Followed by 3 month re-integration & commissioning

- jFEX and L1Topo prototypes at CERN / STF

- Integrated tests currently ongoing

- System level tests starting wk Dec. 10

- L1Topo FDR planned for January 23rd 2019

- L1Topo Production modules available at STF/CERN Mai 2019 (Schedule includes 7 weeks contigency)

- Work towards final installation steps Dec. 2019

JG

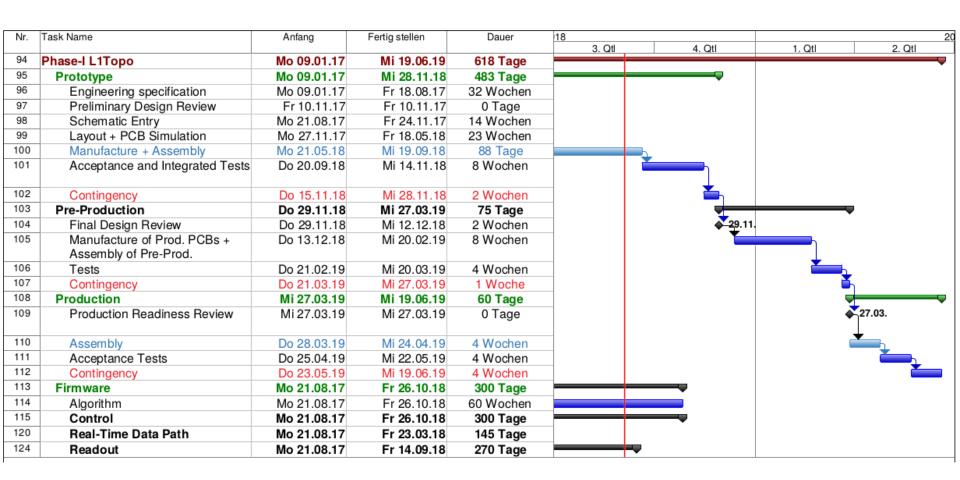

# Back-Up

## Phase-1 L1Topo Schedule

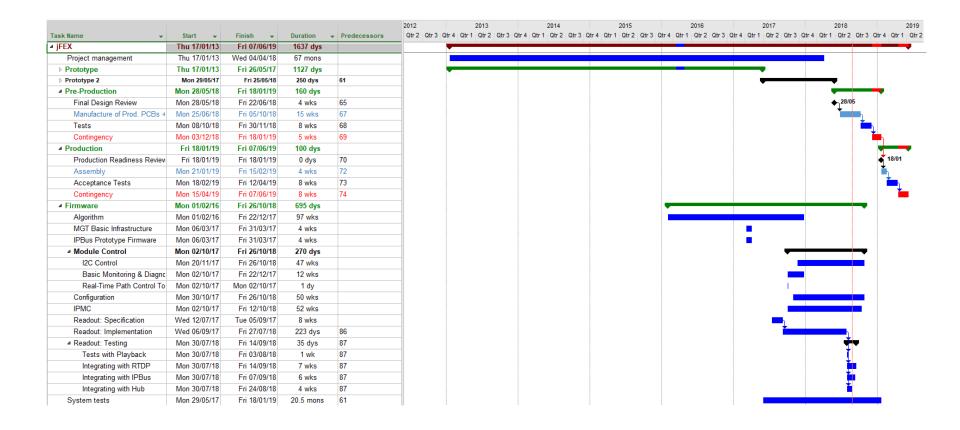

## jFEX Schedule